# FAST FOURIER TRANSFORMS OVER PRIME FIELDS OF LARGE CHARACTERISTIC AND THEIR IMPLEMENTATION ON GRAPHICS PROCESSING UNITS

(Thesis format: Monograph)

by

Davood Mohajerani

Graduate Program in Computer Science

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science

The School of Graduate and Postdoctoral Studies

The University of Western Ontario

London, Ontario, Canada

© Davood Mohajerani 2016

### THE UNIVERSITY OF WESTERN ONTARIO

### School of Graduate and Postdoctoral Studies

### CERTIFICATE OF EXAMINATION

|                      | Examiners:                                                         |

|----------------------|--------------------------------------------------------------------|

| Supervisor:          | Dr. John Barron                                                    |

| Dr. Marc Moreno Maza | Dr. Dan Christensen                                                |

|                      | Dr. Mark Daley                                                     |

| The                  | thesis by                                                          |

| Davood               | Mohajerani                                                         |

| er                   | ntitled:                                                           |

|                      | Fields of Large Characteristic and their Graphics Processing Units |

| requirements         | rtial fulfillment of the s for the degree of r of Science          |

| Date                 | Chair of the Thesis Examination Board                              |

### Abstract

Prime field arithmetic plays a central role in computer algebra and supports computation in Galois fields which are essential to coding theory and cryptography algorithms. The prime fields that are used in computer algebra systems, in particular in the implementation of modular methods, are often of small characteristic, that is, based on prime numbers that fit on a machine word. Increasing precision beyond the machine word size can be done via the Chinese Remainder Theorem or Hensel's Lemma.

In this thesis, we consider prime fields of large characteristic, typically fitting on n machine words, where n is a power of 2. When the characteristic of these fields is restricted to a subclass of the generalized Fermat numbers, we show that arithmetic operations in such fields offer attractive performance both in terms of algebraic complexity and parallelism. In particular, these operations can be vectorized, leading to efficient implementation of fast Fourier transforms on graphics processing units.

**Keywords:** Fast Fourier transforms, finite fields of large characteristic, graphics processing units

### Acknowlegements

First and foremost, I would like to offer my sincerest gratitude to my supervisor Professor Marc Moreno Maza, I am very thankful for his great advice and support.

It is my honor to have Professor John Barron, Professor Dan Christensen, and Professor Mark Daley as the examiners. I am grateful for their insightful comments and questions.

I would like to thank the members of Ontario Research Center for Computer Algebra and the Computer Science Department of the University of Western Ontario. Specially, I am thankful to my colleagues Dr. Ning Xie, Dr. Masoud Ataei, and Egor Chesakov for proofreading chapters of my thesis.

Finally, I am very thankful to my family and friends for their endless support.

### Contents

| Li | st of                  | Algor        | ithms                                                   | viii |

|----|------------------------|--------------|---------------------------------------------------------|------|

| Li | $\operatorname{st}$ of | Figure       | es                                                      | x    |

| Li | ${ m st}$ of           | Table        | ${f s}$                                                 | xii  |

| 1  | Intr                   | oduct        | ion                                                     | 1    |

| 2  | Bac                    | kgrou        | $\mathbf{nd}$                                           | 8    |

|    | 2.1                    | GPGF         | PU computing                                            | 8    |

|    |                        | 2.1.1        | CUDA programming model                                  | 8    |

|    |                        | 2.1.2        | CUDA memory model                                       | 11   |

|    |                        | 2.1.3        | Examples of programs in CUDA                            | 13   |

|    |                        | 2.1.4        | Performance of GPU programs                             | 16   |

|    |                        | 2.1.5        | Profiling CUDA applications                             | 19   |

|    |                        | 2.1.6        | A note on psuedo-code                                   | 20   |

|    | 2.2                    | Fast F       | Fourier Transforms                                      | 21   |

| 3  | Ari                    | ${f thmeti}$ | ic Computations Modulo Sparse Radix Generalized Fermat  |      |

|    | Nui                    | nbers        |                                                         | 24   |

|    | 3.1                    | Repre        | sentation of $\mathbb{Z}/p\mathbb{Z}$                   | 25   |

|    | 3.2                    |              | ng primitive roots of unity in $\mathbb{Z}/p\mathbb{Z}$ | 27   |

|    | 3.3                    | Additi       | ion and subtraction in $\mathbb{Z}/p\mathbb{Z}$         | 28   |

|    | 3.4                    | Multip       | plication by a power of $r$ in $\mathbb{Z}/p\mathbb{Z}$ | 29   |

|    | 3.5                    | Multip       | plication in $\mathbb{Z}/p\mathbb{Z}$                   | 29   |

| 4  | Big                    | Prime        | e Field Arithmetic on GPUs                              | 31   |

|    | 4.1                    | Prelin       | ninaries                                                | 31   |

|    |                        | 4.1.1        | Parallelism for arithmetic in $\mathbb{Z}/p\mathbb{Z}$  | 32   |

|    |                        | 119          | Representing data in $\mathbb{Z}/n\mathbb{Z}$           | 39   |

|   |      | 4.1.3   | Location of data                                           | 33 |

|---|------|---------|------------------------------------------------------------|----|

|   |      | 4.1.4   | Transposing input data                                     | 35 |

|   | 4.2  | Imple   | menting big prime field arithmetic on GPUs                 | 38 |

|   |      | 4.2.1   | Host entry point for arithmetic kernels                    | 38 |

|   |      | 4.2.2   | Implementation notes                                       | 41 |

|   |      | 4.2.3   | Addition and subtraction in $\mathbb{Z}/p\mathbb{Z}$       | 42 |

|   |      | 4.2.4   | Multiplication by a power of r in $\mathbb{Z}/p\mathbb{Z}$ | 45 |

|   |      | 4.2.5   | Multiplication in $\mathbb{Z}/p\mathbb{Z}$                 | 46 |

|   | 4.3  | Profili | ng results                                                 | 55 |

| 5 | Stri | de Per  | rmutation on GPUs                                          | 60 |

|   | 5.1  | Stride  | permutation                                                | 60 |

|   |      | 5.1.1   | GPU kernels for stride permutation                         | 62 |

|   |      | 5.1.2   | Host entry point for permutation kernels                   | 67 |

|   | 5.2  | Profili | ng results                                                 | 68 |

| 6 | Big  | Prime   | e Field FFT on GPUs                                        | 70 |

|   | 6.1  |         | y-Tukey FFT                                                | 70 |

|   | 6.2  |         | plication by twiddle factors                               | 71 |

|   | 6.3  | Implei  | mentation of the base-case DFT-K                           | 73 |

|   |      | 6.3.1   | Expanding DFT-K based on six-step FFT                      | 73 |

|   |      | 6.3.2   | Implementation of DFT-2                                    | 73 |

|   |      | 6.3.3   | Computing DFT-16 based on DFT-2                            | 75 |

|   | 6.4  | Host e  | entry point for computing DFT                              | 86 |

|   |      | 6.4.1   | $FFT-K^2$                                                  | 86 |

|   |      | 6.4.2   | FFT-general based on K                                     | 87 |

|   | 6.5  | Profili | ng results                                                 | 89 |

| 7 | Exp  | erime   | ntal Results: Big Prime Field FFT vs Small Prime Field FFT | 90 |

|   | 7.1  | Backg   | round                                                      | 90 |

|   | 7.2  | Comp    | aring FFT over small and big prime fields                  | 92 |

|   |      | 7.2.1   | Benchmark 1: Comparison when computations produce the same |    |

|   |      |         | amount of output data                                      | 93 |

|   |      | 7.2.2   | Benchmark 2: Comparison when computations process the same |    |

|   |      |         | amount of input data                                       | 93 |

|   | 7.3  | Bench   | mark results                                               | 93 |

|   |      | 7.3.1   | Performance analysis.                                      | 94 |

| 7.4 Concluding remarks                                                          | 97             |

|---------------------------------------------------------------------------------|----------------|

| Bibliography                                                                    | 99             |

| Appendix A Table of 32-bit Fourier primes                                       | 102            |

| Appendix B Hardware specification  B.1 GeforceGTX760M (Kepler)                  | <b>103</b>     |

| Appendix C Source code  C.1 Kernel for computing reverse mixed-radix conversion | <b>105</b> 105 |

| Curriculum Vitae                                                                | 108            |

# List of Algorithms

| 2.1  | Radix $K$ Fast Fourier Transform in $\mathcal{R}$                                                                                                                                                                | 23 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1  | Primitive N-th root $\omega \in \mathbb{Z}/p\mathbb{Z}$ s.t. $\omega^{N/2k} = r$                                                                                                                                 | 27 |

| 3.2  | Computing $x + y \in \mathbb{Z}/p\mathbb{Z}$ for $x, y \in \mathbb{Z}/p\mathbb{Z}$                                                                                                                               | 28 |

| 3.3  | Computing $xy \in \mathbb{Z}/p\mathbb{Z}$ for $x, y \in \mathbb{Z}/p\mathbb{Z}$                                                                                                                                  | 29 |

| 4.1  | $DeviceAddition(\vec{\mathtt{x}},\vec{\mathtt{y}},\mathtt{k},\mathtt{r})  .  .  .  .  .  .  .  .  .  $                                                                                                           | 43 |

| 4.2  | $DeviceSubtraction(\vec{\mathtt{x}},\vec{\mathtt{y}},\mathtt{k},\mathtt{r})\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\$                                                                                             | 44 |

| 4.3  | $DeviceRotation(\vec{\mathtt{x}},\mathtt{k})  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots$                                                                                                            | 45 |

| 4.4  | $DeviceMultPowR(\vec{\mathtt{x}},\mathtt{s},\mathtt{k},\mathtt{r})  .  .  .  .  .  .  .  .  .  $                                                                                                                 | 46 |

| 4.5  | $DeviceMultFinalResult(\vec{1}, \vec{h}, \vec{c}, k, r)  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                                                        | 48 |

| 4.6  | $\label{eq:DeviceIntermediateProduct1([a,b],k:=8,r:=2^{63}+2^{34}) \ \dots $                               | 49 |

| 4.7  | $KernelSequentialPlainMult(\vec{\mathtt{X}},\vec{\mathtt{Y}},\vec{\mathtt{U}},\mathtt{N},\mathtt{k},\mathtt{r})  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  $                       | 51 |

| 4.8  | $DeviceSequentialMult(\vec{\mathtt{x}},\vec{\mathtt{y}},\mathtt{k},\mathtt{r})  .  .  .  .  .  .  .  .  .  $                                                                                                     | 52 |

| 4.9  | $KernelParallelPlainMult(\vec{X},\vec{Y},\vec{U},\vec{L},\vec{H},\vec{C},\mathbb{N},\mathtt{k},\mathtt{r})  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  $                            | 54 |

| 4.10 | $DeviceParallelMult(\vec{\mathtt{x}},\vec{\mathtt{y}},\mathtt{k},\mathtt{r})  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots$                                                                            | 55 |

| 5.1  | $KernelBasePermutationSingleBlock(\vec{\mathtt{X}},\vec{\mathtt{Y}},\mathtt{K},\mathtt{N},\mathtt{k},\mathtt{s},\mathtt{r}) \ \ldots \ $ | 65 |

| 5.2  | $KernelBasePermutationMultipleBlocks(\vec{\mathtt{X}},\vec{\mathtt{Y}},\mathtt{K},\mathtt{N},\mathtt{k},\mathtt{s},\mathtt{r})  \ldots  \ldots  \ldots  \ldots$                                                  | 66 |

| 5.3  | $\mbox{HostGeneralStridePermutation } (\vec{X}, \vec{Y}, K, N, k, s, r, b) \ . \ . \ . \ . \ . \ . \ . \ . \ . \ $                                                                                               | 68 |

| 6.1  | $KernelTwiddleMultiplication(\vec{X},\vec{\Omega},\mathbb{N},K,\mathtt{k},\mathtt{s},\mathtt{r})  \ldots  \ldots  \ldots  \ldots  \ldots$                                                                        | 72 |

| 6.2  | $DeviceDFT2(\vec{\mathtt{X}},\mathtt{i},\mathtt{j},\mathtt{N},\mathtt{k},\mathtt{r})  .  .  .  .  .  .  .  .  .  $                                                                                               | 74 |

| 6.3  | $DeviceDFT16Step1(\vec{\mathtt{X}}, \mathtt{N}, \mathtt{k}, \mathtt{r})  .  .  .  .  .  .  .  .  .  $                                                                                                            | 76 |

| 6.4  | $DeviceDFT16Step2(\vec{\mathtt{X}}, \mathtt{N}, \mathtt{k}, \mathtt{r})  .  .  .  .  .  .  .  .  .  $                                                                                                            | 78 |

| 6.5  | $DeviceDFT16Step3(\vec{\mathtt{X}}, \mathtt{N}, \mathtt{k}, \mathtt{r})  .  .  .  .  .  .  .  .  .  $                                                                                                            | 79 |

| 6.6  | $DeviceDFT16Step4(\vec{\mathtt{X}}, \mathtt{N}, \mathtt{k}, \mathtt{r})  .  .  .  .  .  .  .  .  .  $                                                                                                            | 80 |

| 6.7  | $DeviceDFT16Step5(\vec{\mathtt{X}}, \mathtt{N}, \mathtt{k}, \mathtt{r})  .  .  .  .  .  .  .  .  .  $                                                                                                            | 81 |

| 6.8  | $DeviceDFT16Step6(\vec{\mathtt{X}}, \mathtt{N}, \mathtt{k}, \mathtt{r})  .  .  .  .  .  .  .  .  .  $                                                                                                            | 83 |

| 6.9  | $DeviceDFT16Step7(\vec{\mathtt{X}}, \mathtt{N}, \mathtt{k}, \mathtt{r})  .  .  .  .  .  .  .  .  .  $                                                                                                            | 84 |

| 6.10 | DeviceDFT16Step8( $\vec{X}$ , N, k, r)                                                                                                                                                                           | 85 |

| 6.11 | $KernelBaseDFT16AllSteps(\vec{\mathtt{X}}, \mathtt{N}, \mathtt{k}, \mathtt{r}) \ . \ . \ . \ . \ . \ . \ . \ . \ . \ $                                                                                | 86 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 6.12 | $HostDFTK2(\vec{\mathtt{X}},\vec{\Omega},\mathtt{N},\mathtt{K},\mathtt{k},\mathtt{s},\mathtt{r},\mathtt{b})  .  .  .  .  .  .  .  .  .  $                                                             | 87 |

| 6.13 | $HostDFTGeneral(\vec{\mathtt{X}},\vec{\Omega},\mathtt{N},\mathtt{K},\mathtt{k},\mathtt{s},\mathtt{r},\mathtt{b}) \ \ldots \ $ | 88 |

# List of Figures

| 2.1  | Example of a 2D thread block with 2 rows and 6 columns                        | 9  |

|------|-------------------------------------------------------------------------------|----|

| 2.2  | Example of a 2D grid with 2 rows and 4 columns                                | 10 |

| 2.3  | Host and device in the CUDA programming model                                 | 10 |

| 2.4  | CUDA memory hierarchy for CC 2.0 and higher                                   | 11 |

| 2.5  | A CUDA example for computing point-wise addition of two vectors               | 14 |

| 2.6  | A CUDA example for transposing matrices by using shared memory                | 15 |

| 2.7  | Four independent instructions                                                 | 18 |

| 2.8  | An example of ILP                                                             | 19 |

| 4.1  | The non-transposed input matrix $\mathtt{M}_0.$                               | 35 |

| 4.2  | Indexes of digits in the non-transposed matrix $\mathtt{M}_0.$                | 35 |

| 4.3  | Threads inside a warp reading from the non-transposed input                   | 36 |

| 4.4  | The transposed input matrix $M_1, \ldots, M_n$                                | 36 |

| 4.5  | Indexes of digits in the transposed matrix $\mathtt{M}_1.$                    | 37 |

| 4.6  | Threads inside a warp reading from the transposed input                       | 37 |

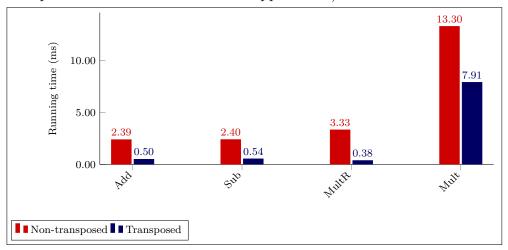

| 4.7  | Diagram of running-time for $N=2^{17}$                                        | 57 |

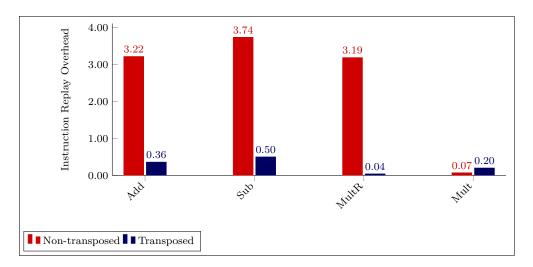

| 4.8  | Diagram of instruction overhead for $N=2^{17}$                                | 58 |

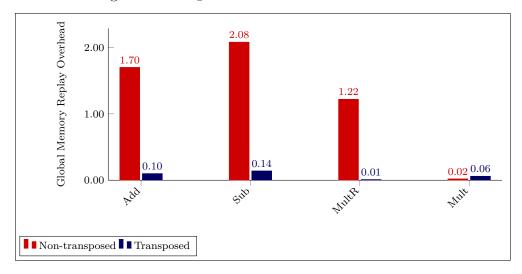

| 4.9  | Diagram of memory overhead for $N=2^{17}$                                     | 58 |

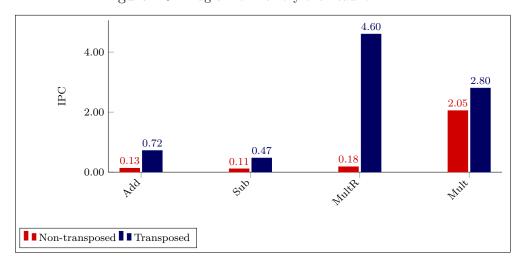

| 4.10 | Diagram of IPC for $N=2^{17}$                                                 | 58 |

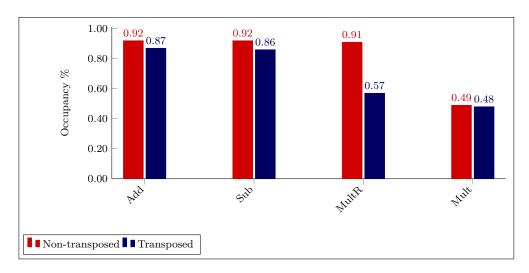

| 4.11 | Diagram of occupancy percentage for $N=2^{17},\ldots,\ldots$                  | 59 |

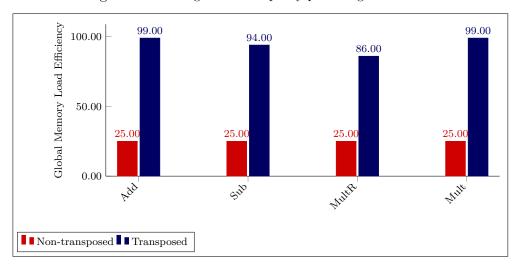

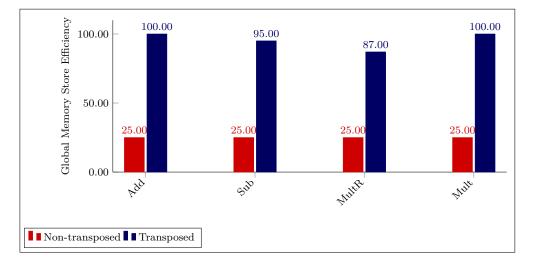

| 4.12 | Diagram of memory load efficiency for $N=2^{17}$                              | 59 |

| 4.13 | Diagram of memory store efficiency for $N=2^{17}$                             | 59 |

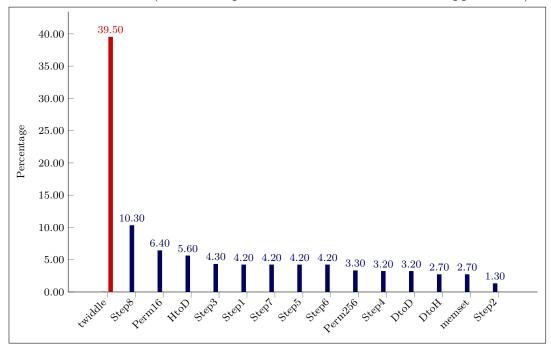

| 5.1  | Profiling results for stride permutation $L_K^{KJ}$ for $K=256$ and $J=4096.$ | 69 |

| 5.2  | Profiling results for stride permutation $L_K^{KJ}$ for $K=16$ and $J=2^{16}$ | 69 |

| 6.1  | Running-time for computing DFT <sub>N</sub> with $N=K^4$ and $K=16.$          | 89 |

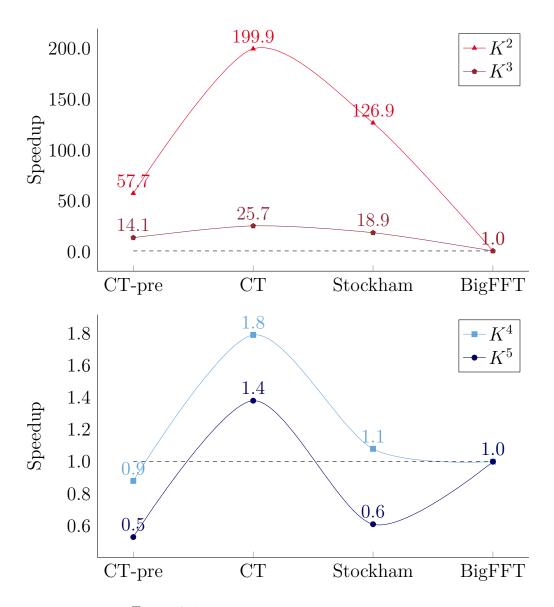

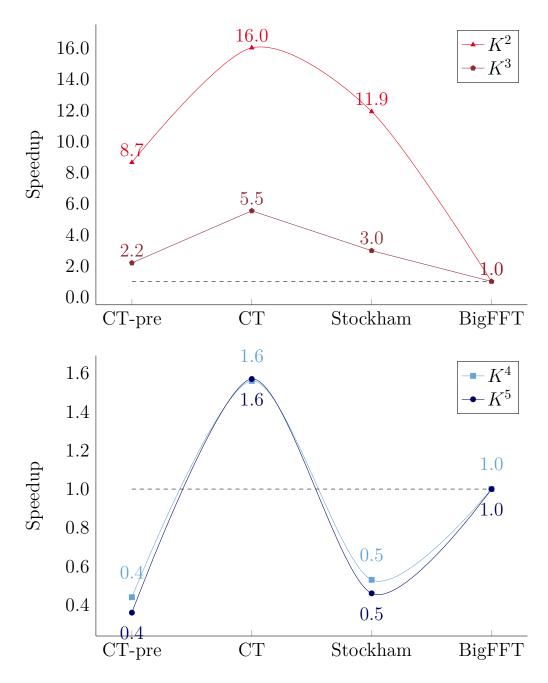

| 7.1  | Speed-up diagram of Benchmark 1 for $K=16.$                                   | 96 |

| 7.2  | Speed-up diagram of Benchmark 2 for $K = 16$                                  | 97 |

| B.1 | Hardware specification for NVIDIA GeforceGTX760M                     | 103 |

|-----|----------------------------------------------------------------------|-----|

| B.2 | The bandwidth test from CUDA SDK (samples/1_Utilites/bandwidthTest). | 104 |

## List of Tables

| 2.1 | The maximum number of warps per streaming multiprocessor       | 11  |

|-----|----------------------------------------------------------------|-----|

| 2.2 | The number of 32-bit registers per streaming multiprocessor    | 12  |

| 2.3 | A short list of performance metrics of nvprof                  | 20  |

| 3.1 | SRGFNs of practical interest                                   | 25  |

| 7.1 | Running time of computing Benchmark 1 for $N=K^2$ with $K=16.$ | 95  |

| 7.2 | Running time of computing Benchmark 1 for $N=K^3$ with $K=16.$ | 95  |

| 7.3 | Running time of computing Benchmark 1 for $N=K^4$ with $K=16.$ | 95  |

| 7.4 | Running time of computing Benchmark 1 for $N=K^5$ with $K=16.$ | 95  |

| 7.5 | Running time of computing Benchmark 2 for $N=K^e$ with $K=16.$ | 95  |

| A.1 | Table of 32-bit Fourier primes                                 | 102 |

### Chapter 1

### Introduction

Prime field arithmetic plays a central role in computer algebra and supports computation in Galois fields which are essential to coding theory and cryptography algorithms. In computer algebra, the so-called *modular methods* are the main application of prime field arithmetic. Let us give a simple example of such methods.

Consider a square matrix A of order n with coefficients in the ring  $\mathbb{Z}$  of integers. It is well-known that  $\det(A)$ , the determinant of A, can be computed in at most  $2n^3$  arithmetic operations in the field  $\mathbb{Q}$  of rational numbers, by means of Gaussian elimination. However the cost of each of those operations is not the same and, in fact, depends on the bit size of the rational numbers involved. It can be proved that, if B is the maximum absolute value of a coefficient in A then computing the determinant of A directly (that is, over  $\mathbb{Z}$ ) can be done within  $\mathcal{O}(n^5 (\log n + \log B)^2)$  machine-word operations, see the landmark book [24]. If a modular method is used, based on the Chinese Remainder Theorem (CRT), one can reduce the cost to  $\mathcal{O}(n^4 \log^2(nB) (\log^2 n + \log^2 B))$  machine-word operations.

Let us explain how this works. Let d be the determinant of A and let us choose a prime number  $p \in \mathbb{Z}$  such that the absolute value |d| of d satisfies

$$2 \mid d \mid < p$$

.

Let r be the determinant of A regarded as a matrix over  $\mathbb{Z}/p\mathbb{Z}$  and let us represent the elements of  $\mathbb{Z}/p\mathbb{Z}$  within the symmetric range  $\left[-\frac{p-1}{2}\cdots\frac{p-1}{2}\right]$ . Hence we have

$$-\frac{p}{2} < r < \frac{p}{2} \text{ and } -\frac{p}{2} < d < \frac{p}{2}$$

(1.1)

leading to

$$-p < d - r < p \tag{1.2}$$

Observe that det(A) is a polynomial expression in the coefficients of A. For instance with n=2 we have

$$\det(A) = a_{11} a_{22} - a_{12} a_{21}. (1.3)$$

Denoting by  $\overline{x}^p$  the residue class in  $\mathbb{Z}/p\mathbb{Z}$  of any  $x \in \mathbb{Z}$ , we have

$$\overline{x+y}^p = \overline{x}^p + \overline{y}^p \quad \text{and} \quad \overline{x}\overline{y}^p = \overline{x}^p \overline{y}^p,$$

(1.4)

for all  $x, y \in \mathbb{Z}$ . It follows for n = 2, and using standard notations, that we have

$$\overline{\det(A)}^p = \overline{a_{11}}^p \, \overline{a_{22}}^p - \overline{a_{12}}^p \, \overline{a_{21}}^p. \tag{1.5}$$

More generally, we have

$$\overline{\det(A)}^p = \det(A \mod p), \tag{1.6}$$

that is,  $d \equiv r \mod p$ . This with Relation (1.2) leads to

$$d = r. (1.7)$$

In summary, the determinant of A as a matrix over  $\mathbb{Z}$  is equal to the determinant of A regarded as a matrix over  $\mathbb{Z}/p\mathbb{Z}$  provided that  $2 \mid d \mid < p$  holds. Therefore, the computation of the determinant of A as a matrix over  $\mathbb{Z}$  can be done modulo p, which provides a way of controlling expression swell in the intermediate computations. See the introduction of Chapter 5 in [23] for a discussion of this phenomenon of expression swell in the intermediate computations.

But if d is what we want to compute, the condition  $2 \mid d \mid < p$  is not that helpful for choosing p. However, Hadamard's inequality tells us that, if B is the maximum absolute value of an entry of A, then we have

$$\mid d \mid \leq n^{n/2} B^n. \tag{1.8}$$

One can then choose a prime number p satisfying  $2n^{n/2}B^n < p$ . Of course, such prime may be very large and thus the expected benefit of controlling expression swell may be limited.

An alternative approach is to consider pairwise different prime numbers  $p_1, \ldots, p_e$  such that their product exceeds  $2n^{n/2}B^n$ , and each of them fits on a machine-word. Then,

computing the determinants of A regarded as a matrix over  $\mathbb{Z}/p_1\mathbb{Z}, \ldots, \mathbb{Z}/p_e\mathbb{Z}$  leads to values  $r_1, \ldots, r_e$ , respectively. Finally, applying the CRT yields d.

The advantage of this alternative approach is that for a prime number p fitting on the machine-word of computer, arithmetic operations modulo p can be implemented efficiently using hardware integer operations.

However, using machine-word size, thus small, prime numbers has also serious inconveniences in certain modular methods, in particular for solving systems of non-linear equations. Indeed, in such circumstances, the so-called *unlucky primes* are to be avoided, see for instance [1, 9].

For an example of a modular method incurring unlucky primes, let us consider the simple problem of computing a Greatest Common Divisor (GCD) of two univariate polynomials with integer coefficients. Let  $f = f_n x^n + \cdots + f_0$  and  $g = g_m x^m + \cdots + g_0$  be polynomials in x, with respective degrees n and m, and with coefficients in a unique factorization domain (UFD) R. The following matrix is called the *Sylvester matrix* of f and g.

Its determinant is an element of R called the *resultant* of f and g. This determinant is usually denoted by  $\operatorname{res}(f,g)$  and enjoys the following property: a GCD h of f and g has degree zero (that is, h is simply an element of R) if and only the  $\operatorname{res}(f,g) \neq 0$  holds. In other words, f and g have a non-trivial GCD (that is, a GCD of positive degree) if and only the  $\operatorname{res}(f,g) = 0$  holds.

Assume now that R is the ring  $\mathbb{Z}$  of the integer numbers and that  $\operatorname{res}(f,g) \neq 0$  holds. Suppose that this latter fact is not known and that one is computing a GCD of f and g by means of a modular method based on the CRT. More precisely, we are computing GCDs of f and g modulo sufficiently many prime numbers  $p_1, \ldots, p_e$ , obtaining polynomials  $h_1, \ldots, h_e$  in  $\mathbb{Z}/p_1\mathbb{Z}[x], \ldots, \mathbb{Z}/p_e\mathbb{Z}[x]$ . If none of the prime numbers  $p_1, \ldots, p_e$  divides  $\operatorname{res}(f/h, g/h)$ , nor the leading coefficients of  $f_n$  and  $g_m$ , then combining  $h_1, \ldots, h_e$  by CRT yields a GCD of f and g (which, under the assumption  $\operatorname{res}(f, g) \neq 0$  turns out to be a constant). However, if one of the prime numbers  $p_1, \ldots, p_e$ , say  $p_i$ , divides  $\operatorname{res}(f/h, g/h)$  (even if it does not divide  $f_n$  nor  $g_m$ ) then  $h_i$  has a positive degree. It follows that  $h_i$  is not a modular image of a GCD of f and g in  $\mathbb{Z}[x]$ . Therefore, this prime  $p_i$  should not be used in our CRT scheme and for this reason is called  $\operatorname{unlucky}$ .

Note that as the coefficients of f and g grow, so will  $\operatorname{res}(f,g)$ . As a consequence, small primes are likely to be unlucky for input data with large coefficients. While there are tricks to overcome the *noise* introduced by unlucky primes, this become a serious computational bottleneck, as raised in [2], in an application of polynomial system solving to Hilbert's 16-th Problem. To summarize, certain modular methods, when applied to challenging problems, require the use of prime numbers that do not necessarily fit on a machine-word. This observation motivates the work presented in this thesis.

In this thesis, we consider prime fields of large characteristic, typically fitting on k machine words, where k is a power of 2. For those modular methods in polynomial system solving that require such big prime numbers, one of the most fundamental operations is the Discrete Fourier transform (DFT) of a polynomial. Here again, we refer to the landmark book [24].

Consider a prime field  $\mathbb{Z}/p\mathbb{Z}$  and N, a power of 2, dividing p-1. Then, the finite field  $\mathbb{Z}/p\mathbb{Z}$  admits a N-th primitive root of unity; let us denote by  $\omega$  such an element of  $\mathbb{Z}/p\mathbb{Z}$ . Let  $f \in \mathbb{Z}/p\mathbb{Z}[x]$  be a polynomial of degree at most N-1. Then, computing the DFT of f at  $\omega$  produces the values of f at the successively powers of  $\omega$ , that is,  $f(\omega^0), f(\omega^1), \ldots f(\omega^{N-1})$ . Using an asymptotically fast algorithm, namely a fast Fourier transform (FFT), this calculation amounts to:

- 1.  $N \log(N)$  additions in  $\mathbb{Z}/p\mathbb{Z}$ ,

- 2.  $(N/2) \log(N)$  multiplications by a power of  $\omega$  in  $\mathbb{Z}/p\mathbb{Z}$ .

If the bit-size of p is k machine words, then

- 1. each addition in  $\mathbb{Z}/p\mathbb{Z}$  costs O(k) machine-word operations,

- 2. each multiplication by a power of  $\omega$  costs  $O(k^2)$  machine-word operations.

Therefore, multiplication by a power of  $\omega$  becomes a bottleneck as k grows.

To overcome this difficulty, we consider the following trick proposed by Martin Fürer

in [12, 13]. We assume that  $N = K^e$  holds for some "small" K, say K = 256 and an integer  $e \geq 2$ . Further, we define  $\eta = \omega^{N/J}$ , with  $J = K^{e-1}$  and assume that multiplying an arbitrary element of  $\mathbb{Z}/p\mathbb{Z}$  by  $\eta^i$ , for any  $i = 0, \ldots, K-1$ , can be done within O(k) machine-word operations. Consequently, every arithmetic operation (addition, multiplication) involved in a DFT of size K, using  $\eta$  as a primitive root, amounts to O(k) machine-word operations. Therefore, such DFT of size K can be performed within  $O(K \log(K) k)$  machine-word operations. As we shall see in Chapter 3, this latter result holds whenever p is a so called generalized Fermat number.

Considering now a DFT of size N at  $\omega$ . Using the factorization formula of Cooley and Tukey,

$$DFT_{JK} = (DFT_J \otimes I_K)D_{J,K}(I_J \otimes DFT_K)L_J^{JK}, \qquad (1.10)$$

see Section 2.2, the DFT of f at  $\omega$  is essentially performed by:

- 1.  $K^{e-1}$  DFT's of size K (that is, DFT's on polynomials of degree at most K-1),

- 2. N multiplications by a power of  $\omega$  (coming from the diagonal matrix  $D_{J,K}$ ) and

- 3. K DFT's of size  $K^{e-1}$ .

Unrolling Formula (2.4) so as to replace  $DFT_J$  by  $DFT_K$  and the other linear operators involved (the diagonal matrix D and the permutation matrix L) one can deduce that a DFT of size  $N = K^e$  reduces to:

- 1.  $e K^{e-1}$  DFT's of size K, and

- 2. (e-1)N multiplication by a power of  $\omega$ .

Recall that the assumption on the cost of a multiplication by  $\eta^i$ , for  $0 \le i < K$ , makes the cost for one DFT of size K to  $O(K \log_2(K) k)$  machine-word operations. Hence, all the DFT's of size K together amount to  $O(e N \log_2(K) k)$  machine-word operations, that is,  $O(N \log_2(N) k)$  machine-word operations. Meanwhile, the total cost of the multiplication by a power of  $\omega$  is  $O(e N k^2)$  machine-word operations, that is,  $O(N \log_K(N) k^2)$  machine-word operations. Indeed, multiplying an arbitrary element of  $\mathbb{Z}/p\mathbb{Z}$  by an arbitrary power of  $\omega$  requires a long multiplication at a the cost  $O(k^2)$  machine-word operations. Therefore, under our assumption, a DFT of size N at  $\omega$  amounts to

$$O(N \log_2(N) k + N \log_K(N) k^2)$$

(1.11)

machine-word operations. When using generalized Fermat primes, we have K=2k. Hence, the second term in the big-oh notation, dominates the first one. Without our assumption, as discussed earlier, the same DFT would run within  $O(N \log_2(N) k^2)$  machine-word operations. Therefore, using generalized Fermat primes brings a speedup factor of  $\log(K)$  w.r.t. the direct approach using arbitrary prime numbers.

At this point, it is natural to ask what would be the cost of a comparable computation using small primes and the CRT. To be precise, let us consider the following problem. Let  $p_1, \ldots, p_k$  pairwise different prime numbers of machine-word size and let m be their product. Assume that N divides each of  $p_1 - 1, \ldots, p_k - 1$  such that the each of fields  $\mathbb{Z}/p_1\mathbb{Z}, \ldots, \mathbb{Z}/p_e\mathbb{Z}$  admits a N-th primitive roots of unity,  $\omega_1, \ldots, \omega_k$ , Then  $\omega = (\omega_1, \ldots, \omega_k)$  is an N-th primitive root of  $\mathbb{Z}/m\mathbb{Z}$ . Indeed, the ring  $\mathbb{Z}/p_1\mathbb{Z} \otimes \cdots \otimes \mathbb{Z}/p_e\mathbb{Z}$  is a direct product of fields. Let  $f \in \mathbb{Z}/m\mathbb{Z}[x]$  be a polynomial of degree N-1. One can compute the DFT of f at  $\omega$  in three steps:

- 1. Compute the images  $f_1, \ldots, f_k$  of f in  $\mathbb{Z}/p_1\mathbb{Z}[x], \ldots, \mathbb{Z}/p_k\mathbb{Z}[x]$ .

- 2. Compute the DFT of  $f_i$  at  $\omega_i$  in  $\mathbb{Z}/p_i\mathbb{Z}[x]$ , for  $i=1,\ldots,k$ ,

- 3. Combine the results using CRT so as to obtain a DFT of f at  $\omega$ .

The first and the third above steps will run within  $O(k \times N \times k^2)$  machine-word operations meanwhile the second one amount to  $O(k \times N \log(N))$  machine-word operations.

These estimates seem to suggest that the big prime field approach is slower than the small prime fields approach by a factor of  $k/\log(K)$ . However, we should keep in mind that k and K are small constants meanwhile N is the only quantity which is arbitrary large. Thus, the factor  $k/\log(K)$  does not mean much, at least theoretically. Moreover, the big prime field FFT approach and the above second step in the small prime field FFT approach have similar memory access patterns and costs. Indeed, they use the same 6-step FFT algorithm. Hence, the above first and third steps are overheads to the small prime field FFT approach in terms of memory access costs.

Therefore, it is hard to compare the computational efficiency of the two approaches by using theoretical arguments only. In other words, experimentation is needed and this is what this thesis is about.

The contributions of this thesis are as follows:

- 1. We present algorithms for arithmetic operations in the "big" prime field  $\mathbb{Z}/p\mathbb{Z}$ , where p is a generalized Fermat number of the form  $p = r^k + 1$  where r fits a machine-word and k is a power of 2.

- 2. We report on an a GPU (Graphics Processing Units) implementation of those algorithms as well as a GPU implementation of an FFT over such big prime field.

- 3. Our experimental results show that

- (a) computing an FFT of size N, over a big prime field for p fitting on k 64-bit machine-words, and

- (b) computing 2k FFTs of size N, over a small prime field (that is, where the prime fits a 32-bit half-machine-word) followed by a combination (i.e. CRT-like) of those FFTs

are two competitive approaches in terms of running time. Since the former approach has the benefits mentioned above (in the area of polynomial system solving), we view this experimental observation as a promising result.

The reasons for a GPU implementation are as follows. First, the model of computations and the hardware performance provide interesting opportunities to implement big prime field arithmetic, in particular in terms of vectorization of the program code. Secondly, highly optimized FFTs over small prime fields have been implemented on GPUs by Wei Pan [17, 18] and we use them in our experimental comparison.

This thesis is organized as follows:

- Chapter 2 gathers background materials on GPU programming and FFTs.

- Chapter 3 presents algorithms for performing additions and multiplications in the big prime field  $\mathbb{Z}/p\mathbb{Z}$ .

- Chapter 4 contains our GPU implementation of the algorithms of Chapter 3.

- Chapter 5 discusses how to efficient implement on GPUs the permutations that are required by FFT algorithms.

- Chapter 6 explains how to take advantage of Coolye-Tukey factorization formula in the context of the trick of Martin Fürer for computing FFTs over the big prime field  $\mathbb{Z}/p\mathbb{Z}$ . A GPU implementation of those ideas follows.

- Chapter 7 reports on the experimental comparison "big vs small" that was mentioned above.

Chapter 3 is based on a preliminary work by Svyatoslav Covanov, a former student of Professor Marc Moreno Maza. A first GPU implementation of the algorithms in Chapters 3 together with a GPU implementation of FFTs over the big prime field  $\mathbb{Z}/p\mathbb{Z}$  was attempted by Dr. Liangyu Chen<sup>1</sup> (a former visiting scholar working with Professor Marc Moreno Maza) but yielded unsatisfactory experimental results.

<sup>1</sup>http://faculty.ecnu.edu.cn/s/187/t/1487/main.jspy

### Chapter 2

### Background

In this chapter, we review the basic principles of GPGPU computing and fast Fourier transforms. First, in Section 2.1, we explain GPGPU computing, and specifically, how we can develop parallel programs in the NVIDIA CUDA programming model. Then, in Section 2.2, we explain *fast Fourier transform* and its related definitions.

### 2.1 GPGPU computing

Parallel programming has always been considered as a difficult task. Among many available platforms, general purpose graphics processing unit (GPGPU) computing has proven to be a cost-effective solution for scientific computing. GPUs are parallel processors that can handle huge amounts of data. This makes GPUs the suitable type of platform for data parallel algorithms. Data-parallelism refers to a type of computation in which the work can be distributed to lots of smaller tasks, with little or no dependency between them. In less than a decade, GPGPU computing has evolved from a cutting edge technology to one of the mainstream solutions for high-end computing, specifically NVIDIA corporation has played a huge role in developing and promoting the CUDA programming model (see [19] for more details). In this section, we explain preliminary definitions and keywords that will be frequently used in relation to the CUDA programming model. Definitions and examples of this chapter are based on [7] and [8].

### 2.1.1 CUDA programming model

Compute Unified Device Architecture, or CUDA, is a programming model and language extension that is developed and supported by NVIDIA corporation. The CUDA platform

provides language extensions in C/C++ and a number of other languages. The main purpose of the CUDA platform is to provide a simplified interface for writing scalable parallel programs that can be easily recompiled on GPU cards of different architectures.

**Thread.** A thread is the smallest computational unit in the CUDA programming model. At the time of execution, every thread will be assigned to one scalar processor. Also, each thread belongs to a thread block. Finally, each thread has a unique index inside its respective thread block, which depending on dimensions of the thread block can be accessed via

- 1. threadldx.x,

- 2. threadldx.y (only if the thread belongs to a 2D or 3D thread block),

- 3. threadldx.z (only if the thread belongs to a 3D thread block).

**Thread block.** A group of threads together form a *thread block*. Each thread block belongs to a grid. Finally, each thread block has a unique index inside its respective grid, which depending on the dimensions of the grid can be accessed via

- 1. blockldx.x,

- 2. blockldx.y (only if the thread block block belongs to a 2D or 3D grid),

- 3. and blockldx.z (only if the thread block belongs to a 3D grid).

Figure 2.1 illustrates an example of a two dimensional thread block with 2 rows and 6 columns.

| Thread Block                   |                                         |                                         |                                |                                |                                |  |  |  |

|--------------------------------|-----------------------------------------|-----------------------------------------|--------------------------------|--------------------------------|--------------------------------|--|--|--|

| ThreadIdx.x=0<br>ThreadIdx.y=0 | ThreadIdx.x=1<br>ThreadIdx.y=0          | ThreadIdx.x=2<br>ThreadIdx.y=0          | ThreadIdx.x=3<br>ThreadIdx.y=0 | ThreadIdx.x=4<br>ThreadIdx.y=0 | ThreadIdx.x=5<br>ThreadIdx.y=0 |  |  |  |

| ~~~~                           |                                         |                                         |                                |                                | *******                        |  |  |  |

| ThreadIdx.x=0<br>ThreadIdx.y=1 | ThreadIdx.x=1<br>ThreadIdx.y=1          | ThreadIdx.x=2<br>ThreadIdx.y=1          | ThreadIdx.x=3<br>ThreadIdx.y=1 | ThreadIdx.x=4<br>ThreadIdx.y=1 | ThreadIdx.x=5<br>ThreadIdx.y=1 |  |  |  |

| ~~~~                           | *************************************** | *************************************** | ~~~~~                          | ******                         | ~~~~                           |  |  |  |

Figure 2.1: Example of a 2D thread block with 2 rows and 6 columns.

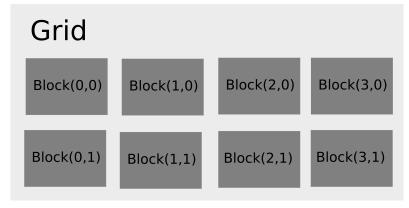

**Grid.** A group of independent thread blocks together form a *grid.* CUDA-capable GPUs can support 2D or 3D grids (depending on their architecture). Figure 2.2 illustrates an

example of a two dimensional block with 2 rows and 4 columns.

Figure 2.2: Example of a 2D grid with 2 rows and 4 columns.

**Kernel.** At the time of execution, all threads in all thread blocks will run the same function. which is known as *Kernel*.

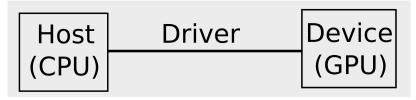

**Device.** In the CUDA programming model, *device* refers to the GPU that executes kernels on threads.

**Host.** In the CUDA programming model, *host* refers to the CPU that initializes kernels. Figure 2.3 shows the relationship between the host and the device.

Figure 2.3: Host and device in the CUDA programming model.

Compute capability (CC). Every CUDA device is built on a core architecture with some specific capabilities. Each device is numbered by a Compute capability (CC), which is of the form A.B. This numbering makes it easier to distinguish architectures from each other. In this presentation, A as the major part, specifies the architecture series, and B, as the minor part, relates to the special improvements to each architecture. For example, devices of compute capability 3.0, 3.1, and 3.2 have the same architecture core, however, they have different hardware optimizations.

Warp. Every 32 threads inside a thread block form a warp.

**Streaming multiprocessor.** Streaming multiprocessors (SMs) are building blocks of GPUs. Each streaming multiprocessor has a number of scalar processors, registers, warp

schedulers, and cache. At the time of execution, the device driver will assign each thread block to one streaming multiprocessor. After being scheduled by the warp scheduler, each thread of the thread block will run the kernel on one processing core.

Warp scheduler. At the time of execution, each streaming multiprocessor partitions threads into warps. In the next step, warps will be scheduled by a warp scheduler for execution on scalar processors. Table 2.1 shows the maximum number of warps that can reside on streaming multiprocessors of different compute capabilities.

| Compute capability                   | 1.0/1.1 | 1.2/1.3 | 2.x  | 3.x and higher |

|--------------------------------------|---------|---------|------|----------------|

| The maximum number of threads per SM | 768     | 1024    | 1536 | 2048           |

| The maximum number of warps          | 24      | 32      | 48   | 64             |

Table 2.1: The maximum number of warps per streaming multiprocessor.

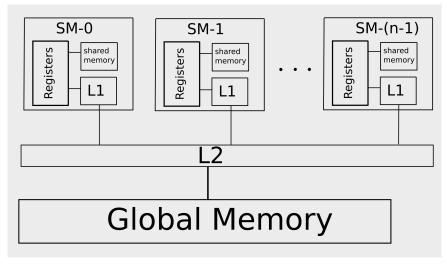

#### 2.1.2 CUDA memory model

The CUDA platform has multiple levels of memory. As a programmer, it is critical to use different types of GPU memory properly. In other words, each level of GPU memory should be used for a specific type of application. Figure 2.4 shows levels of GPU memory for devices of compute capability 2.0 and higher.

Figure 2.4: CUDA memory hierarchy for CC 2.0 and higher.

**On-chip memory.** This type of memory is located on the streaming multiprocessor. Registers, shared memory, and L1 cache are examples of on-chip memory. All other levels of GPU memory are considered as *off-chip memory*.

**Registers.** Registers are fastest type of memory on GPUs. Accessing to a register has almost no cost, because it is placed on the streaming multiprocessor. Each streaming multiprocessor has a limited number of registers. Table 2.2 shows the number of available registers on one streaming multiprocessor for CUDA-capable NVIDIA GPUs.

| Compute capability                | 1.x | 2.x | 3.x | 4.x | 5.x | 6.x |

|-----------------------------------|-----|-----|-----|-----|-----|-----|

| The number of 32-bit registers/SM | 124 | 63  | 255 | 255 | 255 | 255 |

Table 2.2: The number of 32-bit registers per streaming multiprocessor.

**Global memory.** This type of memory is available to all threads in all thread blocks. Global memory is the slowest type of GPU memory.

Coalesced accesses to global memory. Inside a warp, consecutive threads can have access to consecutive words in global memory in a *coalesced* way. For doing so, the GPU driver translates multiple read or write memory calls into a single memory call. For current CUDA-enabled GPUs,

**L1 Cache.** This type of on-chip GPU memory is accessible by all threads inside a warp. GPUs have comparably less amount of L1 cache per multiprocessor than CPUs have. Depending on the GPU architecture (CC), the programmer can enable or disable the L1 caching.

**L2 Cache.** This type of off-chip GPU memory is available on devices of compute capability 2.0 and higher. If L1 cache is enabled, all read requests to global memory will first go through the L1 cache, and then through the L2 cache. However, if the L1 cache is disabled, all read transactions will go directly through the L2 cache.

**Local memory.** Each thread can have a private off-chip memory, known as *local memory*. Local memory is allocated on global memory, therefore, accesses to local memory will be slow. However, accesses to local memory will be coalesced if adjacent threads of the same warp will have access to the same index of an array. Devices of compute capability 1.x have 16 KB of local memory. Finally, devices of other compute capabilities have 512 KB of local memory.

**Shared memory.** This type of memory is available to all threads inside the thread block. It can be used

- 1. for communicating between threads inside the thread block, and

- 2. as a low cost memory (similar to registers) for storing temporary variables of each thread.

On the positive side, accesses to shared memory have almost no cost, because, compared to registers, it only takes a few more cycles. On the negative side, shared memory accesses can go through bank conflicts, meaning that all accesses will be serialized.

Constant memory. This type of read-only memory is accessible to all threads of a grid and can be used for storing constant data. In order to use constant memory efficiently, all accesses should be to the same memory address at the same time. Otherwise, memory requests will be serialized. Currently, the total amount of constant memory for GPUs of all compute capabilities is equal to 64 KB.

**Texture memory.** This is another type of read-only memory and similar to constant memory, can be used for storing constant data. However, unlike constant memory, scattered to constant memory will not be serialized.

#### 2.1.3 Examples of programs in CUDA

In this section, we present two simple examples of programming in the CUDA-C/C++.

Simple vector addition in CUDA. Figure 2.5 presents a pseudo-code for computing vector addition on GPUs in the following way:

- 1. First, the program allocates host memory for host\_a, host\_b as input array, and for host\_c as the output array. (L16:L18)

- 2. The program reads input data from files into host\_a and host\_b, respectively (L21:L22).

- 3. In next step, the program allocates *device* memory for device\_a, device\_b, device\_c (L25:L27).

- 4. Then, the program copies input vectors from host memory to device memory.

- 5. The program sets dimensions of the thread block and grid block, respectively (L34 and L37).

- 6. At this point, the program invokes the CUDA kernel simpleVectorAddition (L40).

- 7. Now, inside the kernel, each thread computes its index with respect to its thread block index and size of the thread block, and then, it computes the result of addition for two elements of the same relative index from each input array (L4:L5).

- 8. After completing the computation by the device, the program copies back the result of computation into the output array, host\_c (L44).

Naive matrix transposition in CUDA. In this example, we explain how we can transpose a  $16 \times 16$  matrix by using shared memory of GPUs. For an input array of

```

1 __global__ void simpleVectorAddition

2 (int* device_a, int* device_b, int* device_c, int n)

3 { /* computing the thread index */

4 int tid = blockIdx.x*blockDim.x + threadIdx.x;

5 if (tid < n) { device_c[tid] = device_b[tid] + device_a[tid];}</pre>

6 }

7 int main (int argc, char**argv)

8 {

9 /* pointers to host memory */

int *host_a, *host_b, *host_c;

11 /* pointers to device memory */

int *device_a, *device_b, *device_c;

13 /* size of input vector */

int n = 1024*1024;

14

/* allocating arrays on the host memory */

15

host_a = (int*)malloc(sizeof(int)*n);

host b = (int*)malloc(sizeof(int)*n);

17

18 host_c = (int*)malloc(sizeof(int)*n);

/* reading input vectors from files a.dat and b.dat,

respectively.*/

20 host_a = readInputFromFile("a");

21 host_b = readInputFromFile("b");

/* allocating arrays on the device memory */

cudaMalloc( (void**)&device_a, n*sizeof(int));

cudaMalloc( (void**)&device_b, n*sizeof(int));

24

cudaMalloc( (void**)&device_c, n*sizeof(int));

25

/* copy data from the host to the device memory */

26

cudaMemcpy(device_a, a, sizeof(int)*n, cudaMemcpyHostToDevice)

cudaMemcpy(device_b, b, sizeof(int)*n, cudaMemcpyHostToDevice)

//setting up dimensions of a thread block

dim3 blockDim = (512,1,1);

//setting up dimensions of the grid

31

dim3 gridDim = (n/blockDim.x,1,1);

//invoking the kernel from host

33

simpleVectorAddition <<< gridDim, blockDim >>>

(device_a, device_b, device_c,n);

36 //copy back the results from device memory to host memory

cudaMemcpy(host_c, device_c, sizeof(int)*n,

cudaMemcpyDeviceToHost);

return 0;

38

39 }

```

Figure 2.5: A CUDA example for computing point-wise addition of two vectors.

```

1 #define BLOCK SIZE 512

2 // tranposing an array of matrices,

3 // each of size 16x16

4 __global__ void matrix_transposition_16

5 (int* device_x, int* device_y, int n)

6 { /* computing the thread index */

int tid = blockIdx.x*blockDim.x + threadIdx.x;

shared int sharedMem[BLOCK_SIZE];

int total=0;

if (tid < n) { sharedMem[threadIdx.x] = device_x[tid];}</pre>

10

__syncthreads();

11

12 if (tid<n){

i = threadIdx/16;

13

j = threadIdx % 16;

14

15

offsetOut = i + 16j;

device y[tid]=sharedMem[offsetOut]; //y(j,i):=x(i,j)

17

}

18 }

```

Figure 2.6: A CUDA example for transposing matrices by using shared memory.

size n, our example computes transposition for n/256 matrices. We assume that the kernel configuration is similar to that of the previous example. This kernel computes the transposition in the following way.

- 1. Each thread computes its index with respect to its thread block index and size of the thread block (L7).

- 2. In the next step, a shared array of size BLOCK\_SIZE is allocated for all threads of the thread block (L8).

- 3. Then, each thread reads its corresponding value from the input vector into its respective shared memory address (L10).

- 4. The barrier syncthreads() synchronizes all threads of the thread block (L11).

- 5. At this step, each thread computes the row number and the column number of its corresponding value in the input vector, namely, (i, j) (L13 and L14).

- 6. In the next step, each thread computes the offset for its corresponding memory address in output vector, namely, (j, i) (L15).

- 7. Finally, each thread writes its corresponding value to the output vector (L16).

Notice that this kernel does not result in an efficient transposition, because it will have shared memory bank conflicts. It is only mentioned as an illustrative example.

#### 2.1.4 Performance of GPU programs

**Bandwidth.** Bandwidth refers to the rate of transferring data between two memory addresses (that might be in different levels). Theoretical bandwidth is the maximum value for the GPU memory bandwidth which can be calculated by  $B_T = f \times w \times 2$  with

- 1. f as the clock frequency of the GPU memory, and

- 2. w as the width of memory interface (in terms of number of bytes).

For example, for a GPU memory with the clock rate of 1 GHZ and the memory interface of 384 bits wide, we have

$$B_T = 1 \times 10^9 \times \frac{384}{8} \times 2 = 96 \text{ GB/s}.$$

**Practical bandwidth.** Practical (effective) bandwidth is the bandwidth that can be achieved on a GPU in practice. Practical bandwidth can be computed by

$$B_E = \frac{(d_r + d_w)}{t} \tag{2.1}$$

where

- 1.  $d_r$  is the amount of data that is being read from the memory,

- 2.  $d_w$  is the amount of data that is written to the memory, and

- 3. t is the elapsed time for reading from the memory and writing to the memory.

For example, if the program spends 4 milliseconds for copying a vector of  $N = 2^{20}$  long integers (each of size of 8 machine-words) to another vector, then effective bandwidth is

$$B_E = \frac{((2^{20} \times 8 \times 8) \times 2)}{(4 \times 10^{-3})} = 33.5 \text{ GB/s}.$$

Value of practical bandwidth is always less than the value of theoretical bandwidth. Also, enabling some error correction features (like Error-Correcting-Code in NVIDIA cards) can further reduce the effective bandwidth.

Occupancy. Occupancy refers to the ratio of the total number of running warps to the maximum number of warps that can be concurrently executed on each streaming multiprocessor. Following factors can affect the percentage of achieved occupancy:

- 1. the amount of shared memory per each streaming multiprocessor,

- 2. the number of registers per each thread,

- 3. the occurrence of register spilling, and finally,

4. the size of a thread block (which we would prefer to be a multiple of 32).

**Data latency.** This term refers to the time spent between requesting the data by a warp and when the data is ready to be processed by the warp. During this time, the warp scheduler executes another warp, therefore, the requesting warp should be waiting. We try to hide the data latency by increasing the occupancy percentage.

Register spilling. As long as there are enough registers left to be allocated, single variables and constant values will always be stored in registers. However, an array inside a thread will not always be stored in registers. In fact, the compiler makes the decision to store an array in registers of the streaming multiprocessor only if the following conditions are met:

- the compiler should be able to determine the indexes of the array, and

- there should be enough number of registers to allocate to the array.

Otherwise, the array will be stored in local memory, which will result in register spilling. As we explained before, accesses to local memory is costly, therefore, register spilling will have a negative impact on the memory bandwidth. Also, even if the register spilling does not happen, allocating too many registers to each thread will lower the number of concurrent warps, and consequently, will lower the overall occupancy of the application.

**Shared memory bank conflicts.** Shared memory is divided into partitions of the same size, namely, *shared memory banks*. The default size of a shared memory bank is 32 bits, however, for devices of compute capability 2.0 and higher, size of shared memory banks can be configured to 64 bits. Inside a warp, multiple accesses to the same address of shared memory will result in *shared memory bank conflicts*. As a result, conflicted accesses will be serialized, and therefore, will lower the bandwidth.

Arithmetic bound kernels. Arithmetic bound kernels spend most of the computation time for issuing arithmetic instructions. In other words, performance is limited by the high number of arithmetic instructions that should be issued at each clock cycle. For an arithmetic bound kernel, we would prefer to lower warp divergence and therefore, avoid using if-else statements as much as possible. Also, we can balance the computation among arithmetic units of each streaming multiprocessor. For example, we can compute part of the integer arithmetic to the floating point arithmetic units and Special Function Units (SFUs).

**Memory bound kernels.** A kernel is memory bound if it spends most of the time for issuing memory requests. As a result, performance will be limited by memory overheads.

An effective solution for increasing performance of memory bound kernels is to make sure the data latency is minimized and more warps will be concurrently executed. In other words, occupancy should be increased to hide the latency. Also, we must ensure that accesses to global memory are minimized by

- 1. storing data in a data structure that facilitates coalesced accesses, and

- 2. (if possible) reusing the same data for more computations.

As a final note, for a memory bound GPU kernel, the practical bandwidth is usually close to the peak of the theoretical bandwidth.

**Arithmetic intensity.** Arithmetic intensity is defined as the ratio of the number of arithmetic instructions to the total amount of processed data. More importantly, this term does not have a unique definition. For example, we can define the total amount of processed data

- 1. as the total number of memory instructions, or

- 2. as the amount of data in terms of bytes.

Instruction level parallelism (ILP). This term refers to the parallelization of independent instructions at the level of hardware. For example, assume that  $a_i, b_i, c_i$ ( $0 \le i < 4$ ) are pointers to non-overlapping addresses in the memory. Then, as shown in Figure 2.7, we can concurrently compute 4 additions  $a_i := b_i + c_i$  by using 4 threads.

| tid         | 0                 | 1                 | 2                 | 3                 |

|-------------|-------------------|-------------------|-------------------|-------------------|

| Instruction | $a_0 = b_0 + c_0$ | $a_1 = b_1 + c_1$ | $a_2 = b_2 + c_2$ | $a_3 = b_3 + c_3$ |

Figure 2.7: Four independent instructions.

On the other hand, as shown in Figure 2.8, one thread can be used for computing all four additions. However, in practice, it is very difficult to exploit the ILP, mostly because the programmer does not have direct control over it. In fact, it is the compiler that makes the decision for using ILP. Depending on the architecture of the device, 2 or 4 instructions might be parallelized in this way.

| tid         | 0                                                                  |

|-------------|--------------------------------------------------------------------|

|             | $a_0 = b_0 + c_0$                                                  |

| Instruction | $\begin{vmatrix} a_0 = b_0 + c_0 \\ a_1 = b_1 + c_1 \end{vmatrix}$ |

|             | $a_2 = b_2 + c_2$                                                  |

|             | $a_3 = b_3 + c_3$                                                  |

Figure 2.8: An example of ILP.

#### 2.1.5 Profiling CUDA applications

**Profiler.** A profiler is software that is used for inspecting the performance of an application. As part of the software development kit (CUDA-SDK), NVIDIA corporation provides nvprof as the official command-line profiler for CUDA applications. In next step, we explain a number of the most important metrics that can be measured by this profiler. Moreover, Table 2.3 shows a list of the nvprof metrics that will be used for measuring the performance of our implementation.

Instruction per cycle (IPC). This metric measures the total number of instructions that are issued on each streaming multiprocessor at each clock cycle.

Achieved occupancy. This metric represents the ratio of the total number of running warps to the maximum possible number of the warps that can be executed on the multiprocessor.

**Instruction replay overhead.** This metric represents the following ratio:

$$\frac{N_{(issued)} - N_{(requested)}}{N_{(requested)}}$$

(2.2)

where:

- 1.  $N_{(issued)}$  is the total number of issued instructions, and

- 2.  $N_{(requested)}$  is the total number of requested instructions.

There are similar "replay overhead" metrics for some other instructions, for example, global memory replay overhead and shared memory replay overhead measure overheads of global memory and shared memory instructions, respectively.

Global memory load and store throughput. This metric measures the throughput for all global memory load and store transactions, including accesses to the L1 cache and to the L2 cache.

**DRAM read and write throughput.** This metric measures the memory throughput for memory read transactions between the device memory and the L2 cache.

| Metric name           | description                                          |  |

|-----------------------|------------------------------------------------------|--|

| $achieved\_occupancy$ | Percentage of occupancy for all SMs                  |  |

| ipc                   | Instruction per cycle                                |  |

| gst_throughput        | Global memory store throughput                       |  |

| gld_throughput        | Global memory load throughput                        |  |

| gst_efficiency        | Global memory store efficiency                       |  |

| dram_utilization      | Device memory utilization (a value between 0 and 10) |  |

Table 2.3: A short list of performance metrics of nvprof.

#### 2.1.6 A note on psuedo-code.

We present our algorithms in pseudo-codes similar to the CUDA programming model.

**Host** functions. Name of this type of function begins with the keyword Host. Host functions can only be called from the host (CPU). Moreover, this type of function are used for

- 1. initializing the input data, and

- 2. invoking GPU kernels.

**Kernel functions.** The name of this type of function begins with the keyword Kernel. Kernel functions will be loaded on each streaming multiprocessor, then, all threads will execute the same code. Kernel functions can only be called from host functions. Finally, this type of function never returns any values, instead, they only depend on global memory for communicating to the host.

**Device** functions. The name of this type of function begins with the keyword Device. Device functions can only be called from kernel functions. However, device functions can return values to their invoker kernel.

Size of a machine-word. We assume that a machine-word (register) is 64-bits wide.

Fortran style arrays. In this thesis, we present arrays in the following way:

- 1.  $\vec{x}$  refers to vector of digits, each of size of a machine-word,

- 2.  $\vec{\mathbf{x}}[i]$  refers to *i*-th digit of  $\vec{x}$ , and

- 3.  $\vec{x}[i:j]$  refers to *i*-th, ..., *j*-th digits of  $\vec{x}$ .

### 2.2 Fast Fourier Transforms

In this section, we review the Discrete Fourier Transform over a finite field, and its related concepts.

**Primitive and principal roots of unity.** Let  $\mathcal{R}$  be a commutative ring with units. Let N > 1 be an integer. An element  $\omega \in \mathcal{R}$  is a *primitive* N-th root of unity if for  $1 < k \le N$  we have  $\omega^k = 1 \iff k = N$ . The element  $\omega \in \mathcal{R}$  is a *principal* N-th root of unity if  $\omega^N = 1$  and for all  $1 \le k < N$  we have

$$\sum_{j=0}^{N-1} \omega^{jk} = 0. {(2.3)}$$

In particular, if N is a power of 2 and  $\omega^{N/2} = -1$ , then  $\omega$  is a principal N-th root of unity. The two notions coincide in fields of characteristic 0. For integral domains every primitive root of unity is also a principal root of unity. For non-integral domains, a principal N-th root of unity is also a primitive N-th root of unity unless the characteristic of the ring  $\mathcal{R}$  is a divisor of N.

The discrete Fourier transform (DFT). Let  $\omega \in \mathcal{R}$  be a principal N-th root of unity. The N-point DFT at  $\omega$  is the linear function, mapping the vector  $\vec{a} = (a_0, \ldots, a_{N-1})^T$  to  $\vec{b} = (b_0, \ldots, b_{N-1})^T$  by  $\vec{b} = \Omega \vec{a}$ , where  $\Omega = (\omega^{jk})_{0 \le j,k \le N-1}$ . If N is invertible in  $\mathcal{R}$ , then the N-point DFT at  $\omega$  has an inverse which is 1/N times the N-point DFT at  $\omega^{-1}$ .

The fast Fourier transform. Let  $\omega \in \mathcal{R}$  be a principal N-th root of unity. Assume that N can be factorized to JK with J, K > 1. Recall Cooley-Tukey factorization formula [6]

$$DFT_{JK} = (DFT_J \otimes I_K)D_{J,K}(I_J \otimes DFT_K)L_J^{JK}, \qquad (2.4)$$

where, for two matrices A, B over  $\mathcal{R}$  with respective formats  $m \times n$  and  $q \times s$ , we denote by  $A \otimes B$  an  $mq \times ns$  matrix over  $\mathcal{R}$  called the tensor product of A by B and defined by

$$A \otimes B = [a_{k\ell}B]_{k,\ell}$$

with  $A = [a_{k\ell}]_{k,\ell}$  (2.5)

In the above formula,  $DFT_{JK}$ ,  $DFT_{J}$  and  $DFT_{K}$  are respectively the N-point DFT at  $\omega$ , the J-point DFT at  $\omega^{K}$  and the K-point DFT at  $\omega^{J}$ . The stride permutation matrix  $L_{J}^{JK}$  permutes an input vector  $\mathbf{x}$  of length JK as follows

$$\mathbf{x}[iJ+j] \mapsto \mathbf{x}[jJ+i],$$

(2.6)

for all  $0 \le j < J$ ,  $0 \le i < K$ . If **x** is viewed as an  $K \times J$  matrix, then  $L_J^{JK}$  performs a transposition of this matrix. The diagonal twiddle matrix  $D_{JK}$  is defined as

$$D_{J,K} = \bigoplus_{j=0}^{J-1} \operatorname{diag}(1, \omega^j, \dots, \omega^{j(K-1)}), \tag{2.7}$$

Formula (2.4) implies various divide-and-conquer algorithms for computing DFTs efficiently, often referred as fast Fourier transforms (FFTs). See the seminal papers [20] and [11] by the authors of the SPIRAL abd FFTW projects, respectively. This formula also implies that, if K divides J, then all involved multiplications are by powers of  $\omega^K$ .

In the factorization of the matrix DFT<sub>JK</sub>, viewing the size K as a base case and assuming that J is a power of K, Formula (2.4) translates into Algorithm 2.1. In this algorithm, as in the sequel of this section,  $\omega \in \mathcal{R}$  be a principal N-th root of unity and  $(\alpha_0 \alpha_1 ... \alpha_{N-1})$  is a vector whose coefficients are in  $\mathcal{R}$ .

#### **Algorithm 2.1** Radix K Fast Fourier Transform in $\mathcal{R}$

```

procedure FFT_{radix \ K}((\alpha_0\alpha_1...\alpha_{N-1}), \ \omega, \ N=J\cdot K)

for 0 \le j < J do

▶ Data transposition

for 0 \le k < K do

\gamma[j][k] := \alpha_{k,l+j}

end for

end for

for 0 \le j \le J do

▷ Base case FFTs

c[j] := FFT_{base-case}(\gamma[j], \omega^J, K)

end for

for 0 \le k < K do

▶ Twiddle factor multiplication

for 0 \le j \le J do

\delta[k][j] := c[j][k] * \omega^{jk}

end for

end for

for 0 \le k < K do

▶ Recursive calls

\delta[k] = \text{FFT}_{\text{radix } K}(\delta[k], \omega^K, J)

end for

for 0 \le k < K do

▶ Data transposition

for 0 \le j < J do

\alpha[jK + k] := \delta[k][j]

end for

end for

return (\alpha_0\alpha_1...\alpha_{N-1})

end procedure

```

The recursive formulation of Algorithm 2.1 is not appropriate for generating code targeting many-core GPU-like architectures for which, formulating algorithms iteratively facilates the division of the work into kernel calls and thread-blocks.

To this end, we shall unroll Formula (2.4). This will be done in Chapter 6.

### Chapter 3

# Arithmetic Computations Modulo Sparse Radix Generalized Fermat Numbers

The *n*-th Fermat number, denoted by  $F_n$ , is given by  $F_n = 2^{2^n} + 1$ . This sequence plays an important role in number theory and, as mentioned in the introduction, in the development of asymptotically fast algorithms for integer multiplication [21, 13].

Arithmetic operations modulo a Fermat number are simpler than modulo an arbitrary positive integer. In particular 2 is a  $2^{n+1}$ -th primitive root of unity modulo  $F_n$ . Unfortunately,  $F_4$  is the largest Fermat number which is known to be prime. Hence, when computations require the coefficient ring be a field, Fermat numbers are no longer interesting. This motivates the introduction of other family of Fermat-like numbers, see, for instance, Chapter 2 in the text book *Guide to elliptic curve cryptography* [14].

Numbers of the form  $a^{2^n} + b^{2^n}$  where a > 1,  $b \ge 0$  and  $n \ge 0$  are called *generalized Fermat numbers*. An odd prime p is a generalized Fermat number if and only if p is congruent to 1 modulo 4. The case b = 1 is of particular interest and, by analogy with the ordinary Fermat numbers, it is common to denote the generalized Fermat number  $a^{2^n} + 1$  by  $F_n(a)$ . So 3 is  $F_0(2)$ . We call a the radix of  $F_n(a)$ . Note that, Landau's fourth problem asks if there are infinitely many generalized Fermat primes  $F_n(a)$  with n > 0.

In the finite ring  $\mathbb{Z}/F_n(a)\mathbb{Z}$ , the element a is a  $2^{n+1}$ -th primitive root of unity. However, when using binary representation for integers on a computer, arithmetic operations in  $\mathbb{Z}/F_n(a)\mathbb{Z}$  may not be as easy to perform as in  $\mathbb{Z}/F_n\mathbb{Z}$ . This motivates the following.

**Definition 1** We call sparse radix generalized Fermat number, any integer of the form  $F_n(r)$  where r is either  $2^w + 2^u$  or  $2^w - 2^u$ , for some integers  $w > u \ge 0$ . In the former case, we denote  $F_n(r)$  by  $F_n^+(w, u)$  and in the latter by  $F_n^-(w, u)$ .

Table 3.1 lists a few sparse radix generalized Fermat numbers (SRGFNs, for short) that are prime. For each p among those numbers, we give the largest power of 2 dividing p-1, that is, the maximum length N of a vector to which a radix-K FFT algorithm (like Algorithm 2.1) where K is an appropriate power of 2.

| p                             | $\max\{2^e \text{ s.t. } 2^e \mid p-1\}$ |

|-------------------------------|------------------------------------------|

| $(2^{63} + 2^{53})^2 + 1$     | $2^{106}$                                |

| $(2^{64} - 2^{50})^4 + 1$     | $2^{200}$                                |

| $(2^{63} + 2^{34})^8 + 1$     | $2^{272}$                                |

| $(2^{62} + 2^{36})^{16} + 1$  | $2^{576}$                                |

| $(2^{62} + 2^{56})^{32} + 1$  | $2^{1792}$                               |

| $(2^{63} - 2^{40})^{64} + 1$  | $2^{2500}$                               |

| $(2^{64} - 2^{28})^{128} + 1$ | $2^{3584}$                               |

Table 3.1: SRGFNs of practical interest.

**Notation 1** In the sequel of this section, we consider  $p = F_n(r)$ , a fixed SRGFN. We denote by  $2^e$  the largest power of 2 dividing p-1 and we define  $k=2^n$ , so that  $p=r^k+1$  holds.

As we shall see in the sequel of this section, for any positive integer N which is a power of 2 such that N divides p-1, one can find an N-th primitive root of unity  $\omega \in \mathbb{Z}/p\mathbb{Z}$  such that multiplying an element  $a \in \mathbb{Z}/p\mathbb{Z}$  by  $\omega^{i(N/2k)}$  for  $0 \le i < 2k$  can be done in linear time w.r.t. the bit size of a. Combining this observation with an appropriate factorization of the DFT transform on N points over  $\mathbb{Z}/p\mathbb{Z}$ , we obtain an efficient FFT algorithm over  $\mathbb{Z}/p\mathbb{Z}$ .

### 3.1 Representation of $\mathbb{Z}/p\mathbb{Z}$

We represent each element  $x \in \mathbb{Z}/p\mathbb{Z}$  as a vector  $\vec{x} = (x_{k-1}, x_{k-2}, \dots, x_0)$  of length k and with non-negative integer coefficients such that we have

$$x \equiv x_{k-1} r^{k-1} + x_{k-2} r^{k-2} + \dots + x_0 \mod p. \tag{3.1}$$

This representation is made unique by imposing the following constraints

1. either

$$x_{k-1} = r$$

and  $x_{k-2} = \cdots = x_1 = 0$ ,

2. or

$$0 \le x_i < r$$

for all  $i = 0, ..., (k-1)$ .

We also map x to a univariate integer polynomial  $f_x \in \mathbb{Z}[T]$  defined by  $f_x = \sum_{i=0}^{k-1} x_i t^i$  such that  $x \equiv f_x(r) \mod p$ .

Now, given a non-negative integer x < p, we explain how the representation  $\vec{x}$  can be computed. The case  $x = r^k$  is trivially handled, hence we assume  $x < r^k$ . For a non-negative integer z such that  $z < r^{2^i}$  holds for some positive integer  $i \le n = \log_2(k)$ , we denote by vec(z,i) the unique sequence of  $2^i$  non-negative integers  $(z_{2^{i-1}},\ldots,z_0)$  such that we have  $0 \le z_j < r$  and  $z = z_{2^{i-1}}r^{2^{i-1}} + \cdots + z_0$ . The sequence vec(z,i) is obtained as follows:

- 1. if i = 1, we have vec(z, i) = (q, s),

- 2. if i > 1, then vec(z, i) is the concatenation of vec(q, i 1) followed by vec(s, i 1),

where q and s are the quotient and the remainder in the Euclidean division of z by  $r^{2^{i-1}}$ . Clearly,  $\text{vec}(x, n) = \vec{x}$  holds.

We observe that the sparse binary representation of r facilitates the Euclidean division of an non-negative integer z by r, when performed on a computer. Referring to the notations in Definition 1, let us assume that r is  $2^w + 2^u$ , for some integers  $w > u \ge 0$ . (The case  $2^w - 2^u$  would be handled in a similar way.) Let  $z_{\text{high}}$  and  $z_{\text{low}}$  be the quotient and the remainder in the Euclidean division of z by  $2^w$ . Then, we have

$$z = 2^w z_{\text{high}} + z_{\text{low}} = r z_{\text{high}} + z_{\text{low}} - 2^u z_{\text{high}}.$$

(3.2)

Let  $s = z_{\text{low}} + -2^u z_{\text{high}}$  and  $q = z_{\text{high}}$ . Three cases arise:

- (S1) if  $0 \le s < r$ , then q and s are the quotient and remainder of z by r,

- (S2) if  $r \leq s$ , then we perform the Euclidean division of s by r and deduce the desired quotient and remainder,

- (S3) if s < 0, then (q, s) is replaced by (q + 1, s + r) and we go back to Step (S1).

Since the binary representations of  $r^2$  can still be regarded as sparse, a similar procedure can be done for the Euclidean division of an non-negative integer z by  $r^2$ . For higher powers of r, we believe that Montgomery algorithm is the way go, though this remains to be explored.

# 3.2 Finding primitive roots of unity in $\mathbb{Z}/p\mathbb{Z}$

**Notation 2** Let N a power of 2, say  $2^{\ell}$ , dividing p-1 and let  $g \in \mathbb{Z}/p\mathbb{Z}$  be a N-th primitive root of unity.

Recall that such an N-th primitive root of unity can be obtained by a simple probabilistic procedure. Write p=qN+1. Pick a random  $\alpha\in\mathbb{Z}/p\mathbb{Z}$  and let  $\omega=\alpha^q$ . Little Fermat theorem implies that either  $\omega^{N/2}=1$  or  $\omega^{N/2}=-1$  holds. In the latter case,  $\omega$  is an N-th primitive root of unity. In the former, another random  $\alpha\in\mathbb{Z}/p\mathbb{Z}$  should be considered. In our various software implementation of finite field arithmetic [16, 3, 15], this procedure finds an N-th primitive root of unity after a few tries and has never been a performance bottleneck.

In the following, we consider the problem of finding an N-th primitive root of unity  $\omega$  such that  $\omega^{N/2k} = r$  holds. The intention is to speed up the portion of FFT computation that requires to multiply elements of  $\mathbb{Z}/p\mathbb{Z}$  by powers of  $\omega$ .

**Proposition 1** In  $\mathbb{Z}/p\mathbb{Z}$ , the element r is a 2k-th primitive root of unity. Moreover, the following algorithm computes an N-th primitive root of unity  $\omega \in \mathbb{Z}/p\mathbb{Z}$  such that we have  $\omega^{N/2k} = r$  in  $\mathbb{Z}/p\mathbb{Z}$ .

```

Algorithm 3.1 Primitive N-th root \omega \in \mathbb{Z}/p\mathbb{Z} s.t. \omega^{N/2k} = r

procedure Primitive RootAsrootOf(N, r, k, g)

\alpha := g^{N/2k}

\beta := \alpha

j := 1

while \beta \neq r do

\beta := \alpha\beta

j := j + 1

end while

\omega := g^j

return (\omega)

end procedure

```