# Plan

|                          | <ul> <li>&lt; □ &gt; &lt; □ &gt;</li> </ul>    | ★ 돌 ▶ ★ 돌 ▶ 돌 | ୬୯୯    |                                                   | < □ ▶                                                                                    | ◆ 御 ▶ ◆ 臣 ▶ ◆ 臣 ▶ ○ 臣 | 9 Q P  |

|--------------------------|------------------------------------------------|---------------|--------|---------------------------------------------------|------------------------------------------------------------------------------------------|-----------------------|--------|

| (Moreno Maza)            | Parallel Random-Access Machines The PRAM Model | CS3101        | 1 / 66 | (Moreno Maza)                                     | Parallel Random-Access Machines The PRAM Model                                           | CS3101                | 2 / 66 |

| Plan                     |                                                |               |        | The RAM Model                                     |                                                                                          |                       |        |

|                          |                                                |               |        | Recall                                            |                                                                                          |                       | 1      |

| 1 The PRAM Model         |                                                |               |        | The <i>Random Access I</i> computer. Its features | <i>Machine</i> is a convenient model s are as follows.                                   | of a sequential       |        |

| 2 Performance counter    | rs                                             |               |        | •                                                 | <i>unit</i> executes a user defined p<br><i>ly input tape</i> and a <i>write-only</i> of | 0                     |        |

| 3 Handling Shared Me     | mory Access Conflicts: PRAM sub                | omodels       |        |                                                   | unbounded number of local <i>n</i>                                                       |                       |        |

|                          |                                                |               |        | <ul> <li>Each memory cel</li> </ul>               | I can hold an integer of <i>unbou</i>                                                    | nded size.            | - 1    |

| 4) Simulation of large F | PRAMs on small PRAMs                           |               |        |                                                   | et includes operations for: mov                                                          | •                     | - 1    |

| 5 Comparing the Com      | putational Power of PRAM Submo                 | odels         |        | subtractions, mul                                 | mparisons and conditional bran<br>Itiplications.                                         | icning, additions,    |        |

| 6 More PRAM algorith     | nms and exercies                               |               |        |                                                   | with the first instruction of the<br>an Halt instruction is reached                      |                       |        |

|                          | < □ > <月                                       | (B) (B) B     | ৩৫৫    | <ul> <li>Each operation ta<br/>sizes.</li> </ul>  | akes one <i>time unit</i> regardless o                                                   | f the the operand     |        |

| (Moreno Maza)            | Parallel Random-Access Machines                |               | 3 / 66 | (Moreno Maza)                                     | Parallel Random-Access Machines                                                          | CS3101                | 4 / 66 |

The PRAM Model: Definition (1/6)

The PRAM Model

# The PRAM Model: Definition (2/6)

Control

Private Memor

Private Memory

# Architecture

The *Parallel Random Access Machine* is a natural generalization of RAM. It is also an idealization of a *shared memory machine*. Its features are as follows.

- It holds an *unbounded collection of RAM processors*  $P_0, P_1, P_2, ...$  **without tapes**.

- It holds an *unbounded collection of shared memory cells*  $M[0], M[1], M[2], \ldots$

- Each processor  $P_i$  has its own (unbounded) local memory (register set) and  $P_i$  knows its index *i*.

- Each processor  $P_i$  can access any shared memory cell M[j] in *unit time*, unless there is a conflict (see further).

|               | ∢ [                             | u > 《郡 > 《콜 > 《콜 > 콜 · 키익종 |               |                                 | <u>₹</u> ▶ ₹ 9९0 |

|---------------|---------------------------------|----------------------------|---------------|---------------------------------|------------------|

| (Moreno Maza) | Parallel Random-Access Machines | CS3101 5 / 66              | (Moreno Maza) | Parallel Random-Access Machines | CS3101 6 / 66    |

|               | The PRAM Model                  |                            |               | The PRAM Model                  |                  |

|               |                                 |                            |               |                                 |                  |

# The PRAM Model: Definition (3/6)

# Program execution (1/2)

- The input of a PRAM program consists of n items stored in M[0],..., M[n−1].

- The output of a PRAM program consists of n' items stored in n' memory cells, say M[n],..., M[n + n' 1].

- A PRAM instruction executes in a 3-phase cycle:

- **Q** Read (if needed) from a shared memory cell,

- 2 Compute locally (if needed),

- **Write** in a shared memory cell (if needed).

- All processors execute their 3-phase cycles synchronously.

- **Special assumptions** have to be made in order to resolve shared memory access conflicts.

- The only way processors can exchange data is by writing into and reading from memory cells.

# The PRAM Model: Definition (4/6)

# Program execution (2/2)

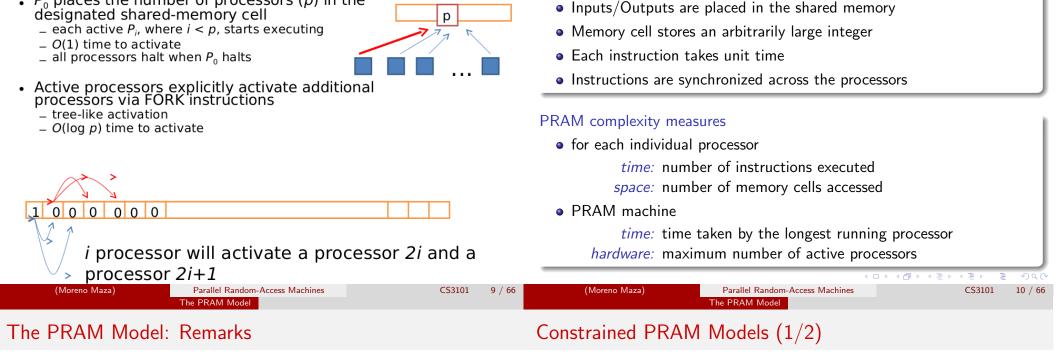

• *P*<sub>0</sub> has a special *activation register* specifying the maximum index of an active processor:

Global

Memory

- 1 Initially, only  $P_0$  is active; it computes the number of required active processors,

- **2** Then,  $P_0$  loads this number in the activation register,

- S The corresponding processors start executing their programs.

- Computations proceed until P<sub>0</sub> halts, at which time all other active processors are halted.

- Parallel time complexity = the time for  $P_0$ 's computations.

- **Parallel space complexity** = the maximum number of shared memory cells in use during the computations.

66

#### The PRAM Model

# The PRAM Model: Definition (5/6)

11 / 66

The PRAM Model is attractive for designing parallel algorithms:

- It is natural: the number of operations executed per one cycle on p processors is at most *p*.

- It is strong: any processor can read or write any shared memory cell in unit time.

- It is simple: ignoring any communication or synchronization overhead.

This natural, strong and simple PRAM model can be used as a benchmark: If a problem has no feasible (or efficient) solution on a PRAM then it is likely that it has no feasible (or efficient) solution on any parallel machine.

- The PRAM model is an idealization of existing shared memory parallel machines.

- The PRAM ignores lower level architecture constraints (memory access overhead, synchronization overhead, intercommunication throughput, connectivity, speed limits, etc.) CS3101 (Moreno Maza)

A *small-memory PRAM* satisfies the axioms of a PRAM except that is has a bounded number of shared memory cells.

- A *m-cell PRAM* is a small-memory PRAM with *m* shared memory cells.

- If the input (or output) data set exceeds the capacity of the shared memory, then this data can be distributed evenly among the registers of the processors.

- Limiting the amount of shared memory corresponds to restricting the amount of information that can be communicated between processors in one step.

- For example, a distributed memory machine with processors interconnected by a shared bus can be modeled as a PRAM with a single shared memory.

(Moreno Maza)

CS3101 12 / 66

3

•  $P_0$  places the number of processors (p) in the

### The PRAM Model

# The PRAM Model: Definition (6/6)

Summary of main assumptions

| The PRAM Model                                                                                                                  | Performance counters                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| Constrained PRAM Models (2/2)                                                                                                   | Plan                                                                                                      |

|                                                                                                                                 |                                                                                                           |

|                                                                                                                                 | 1 The PRAM Model                                                                                          |

| • A <i>small PRAM</i> satisfies the axioms of a PRAM except that is has a bounded number of processors.                         | <ul> <li>Performance counters</li> <li>Bandling Shared Memory Access Conflicts: PRAM submodels</li> </ul> |

| <ul> <li>A <i>p</i>-processor PRAM is a small PRAM with <i>p</i> + 1 processors<br/>(counting <i>P</i><sub>0</sub>).</li> </ul> | ④ Simulation of large PRAMs on small PRAMs                                                                |

|                                                                                                                                 | 5 Comparing the Computational Power of PRAM Submodels                                                     |

|                                                                                                                                 | 6 More PRAM algorithms and exercies                                                                       |

|                                                                                                                                 |                                                                                                           |

|                              | < □ > < □                       | ▶ ▲ 臣 ▶ ▲ 臣 → ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● |               | •                               | 미 🛛 🖉 🕨 🤇 코 🖌 🤇 코 🕨 🖉 코 | E       |

|------------------------------|---------------------------------|---------------------------------------------------|---------------|---------------------------------|-------------------------|---------|

| (Moreno Maza)                | Parallel Random-Access Machines | CS3101 13 / 66                                    | (Moreno Maza) | Parallel Random-Access Machines | CS3101                  | 14 / 66 |

| Performance counters         |                                 | Performance counters                              |               |                                 |                         |         |

| Performance counters $(1/8)$ |                                 | Performance coun                                  | ters (2/8)    |                                 |                         |         |

# Recall

The *Parallel Time*, denoted by T(n, p), is the time elapsed

- from the start of a parallel computation to the moment where the last processor finishes,

- on an input data of size *n*,

- and using *p* processors.

- T(n, p) takes into account

- computational steps (such as adding, multiplying, swapping variables),

- routing (or communication) steps (such as transferring and exchanging information between processors).

### Example 1

Parallel search of an item x

- in an unsorted input file with *n* items,

- in a shared memory with *p* processors,

- where any cell can be accessed by only one processor at a time. Broadcasting x costs  $O(\log(p))$ , leading to

$$T(n,p) = O(\log(p)) + O(n/p).$$

CS3101 15 / 66

-

(日)

# Performance counters (4/8)

# Definition

• The *parallel efficiency*, denoted by E(n, p), is

$$E(n,p)=\frac{SU(n)}{pT(n,p)},$$

where SU(n) is a lower bound for a sequential execution. Observe that we have  $SU(n) \le p T(n, p)$  and thus  $E(n, p) \le 1$ .

• One also often considers the *speedup factor* defined by

$$S(n,p)=\frac{SU(n)}{T(n,p)}$$

### Remark

Reasons for inefficiency:

- large communication latency compared to computational performances (it would be better to calculate locally rather than remotely)

- too big overhead in synchronization, poor coordination, poor load distribution (processors must wait for dependent data),

- lack of useful work to do (too many processors for too little work).

# Performance counters (5/8)

The *Work* is defined by  $W(n, p) = a_{t_{start}} + \cdots + a_{t_{end}}$  where  $a_t$  is the number of active processors a time t.

- A data-processor iso-efficiency function is an asymptotically maximal function  $f_1$  such that for all  $p_0 > 0$  there exists  $n_0$  such that for  $n \ge n_0$  we have  $E(n, f_1(n)) \ge E(n_0, p_0)$ .

- A processor-data iso-efficiency function is an asymptotically minimal function  $f_2$  such that for all  $n_0 > 0$  there exists  $p_0$  such that for  $p \ge p_0$  we have  $E(f_2(p), p) \ge E(n_0, p_0)$ .

- The iso-efficiency function  $f_2$  quantifies the growth rate of the problem size, required to keep the efficiency fixed while increasing the number of processors. It reflects the ability of a parallel algorithm to maintain a constant efficiency. A large iso-efficiency function  $f_2$  indicates poor scalability, whereas a small one indicates that only a small increment in the problem size is sufficient for efficient exploitation of newly added processors.

# Performance counters (6/8)

# Example 2

Consider the following problem: summing *n* numbers on a small PRAM with p < n processors. With the assumption that every "basic" operation runs in unit time, we have SU(n) = n.

- Each processor adds locally  $\left\lceil \frac{n}{p} \right\rceil$  numbers.

- Then the *p* partial sums are summed using a *parallel binary reduction* on p processors in  $\lceil \log(p) \rceil$  iterations.

- Thus, we have:  $T(n,p) \in O(\frac{n}{p} + \log(p))$ .

- Elementary computations give

$$f_1(n) = rac{n}{\log(n)}$$

and  $f_2(p) = p \log(p)$ .

#### Performance counters

# Performance counters (7/8)

#### Performance counters

# Performance counters (8/8)

# Handling Shared Memory Access Conflicts (1/18)

### Definition

- **EREW** (Exclusive Read Exclusive Write): No two processors are allowed to read or write the same shared memory cell simultaneously.

- **CREW** (Concurrent Read Exclusive Write): Simultaneous reads of the same memory cell are allowed, but no two processors can write the same shared memory cell simultaneously.

- **PRIORITY CRCW** (PRIORITY Concurrent Read Conc. Write):

- Simultaneous reads of the same memory cell are allowed.

- Processors are assigned fixed and distinct priorities.

- In case of write conflict, the processor with highest priority is allowed to complete WRITE.

| 6 | More | PRAM | algorithms | and | exercies |

|---|------|------|------------|-----|----------|

Simulation of large PRAMs on small PRAMs

3 Handling Shared Memory Access Conflicts: PRAM submodels

Comparing the Computational Power of PRAM Submodels

| Moreno |  |

|--------|--|

|        |  |

|        |  |

The PRAM Model

Plan

Parallel Random-Access Machines

23 / 66

# Handling Shared Memory Access Conflicts (2/18)

# Definition

**ARBITRARY CRCW** (ARBITRARY Concurrent Read Conc. Write):

- Simultaneous reads of the same memory cell are allowed.

- In case of write conflict, one randomly chosen processor is allowed to complete WRITE.

- An algorithm written for this model should make no assumptions about which processor is chosen in case of write conflict.

### **COMMON CRCW** (COMMON Concurrent Read Conc. Write):

- Simultaneous reads of the same memory cell are allowed.

- In case of write conflict, all processors are allowed to complete WRITE iff all values to be written are equal.

- An algorithm written for this model should make sure that this condition is satisfied. If not, the algorithm is illegal and the machine state will be undefined.

```

(Moreno Maza)

Parallel Random-Access Ma

Handling Shared Memory Access Conflicts: PRAM submodels

```

# Handling Shared Memory Access Conflicts (4/18)

# Concurrent search CREW PRAM algorithm

A similar approach, but  $P_1, P_2, \ldots, P_p$  can read x in O(1). However, the final reduction is still in log(p), leading again to  $T(n,p) = O(\log(p) + \lceil n/p \rceil).$

### Concurrent search COMMON PRAM algorithm

Now, the final step takes O(1). Indeed, those processors with their flag Found equal to true can write simultaneously to the same memory cell initialized to false. Hence, we have  $T(n, p) = O(\lceil n/p \rceil)$ .

#### Handling Shared Memory Access Conflicts: PRAM submodels

# Handling Shared Memory Access Conflicts (3/18)

### Example 4: concurrent search

- Consider a *p*-processor PRAM with p < n.

- Assume that the shared memory contains n distinct items and  $P_0$ owns a value x.

- The goal is to let  $P_0$  know whether x occurs within the *n* items.

### Concurrent search EREW PRAM algorithm

- (a)  $P_0$  broadcasts x to  $P_1, P_2, \ldots, P_p$  in  $O(\log(p))$  steps using binary broadcast tree.

- (b) Every processor  $P_1, P_2, \ldots, P_p$  performs local searches on (at most)  $\lceil n/p \rceil$  items, hence in  $\lceil n/p \rceil$  steps.

- (c) Every processor defines a Boolean flag Found. The final answer is obtained by a *parallel reduction*, that is by, means of a binary tree.

- This leads to  $T(n, p) = O(\log(p) + \lceil n/p \rceil)$ .

| Handling Shared Memory Access Conflicts: PRAM submodels   | lachines | CS3101 | 25 / 66 | (Moreno Maza) | Parallel Random-Access Machines | CS3101 | 26 / 66 |

|-----------------------------------------------------------|----------|--------|---------|---------------|---------------------------------|--------|---------|

| Thinking Shared Memory Recess Comments. The Win Sabinotes |          |        |         |               |                                 |        |         |

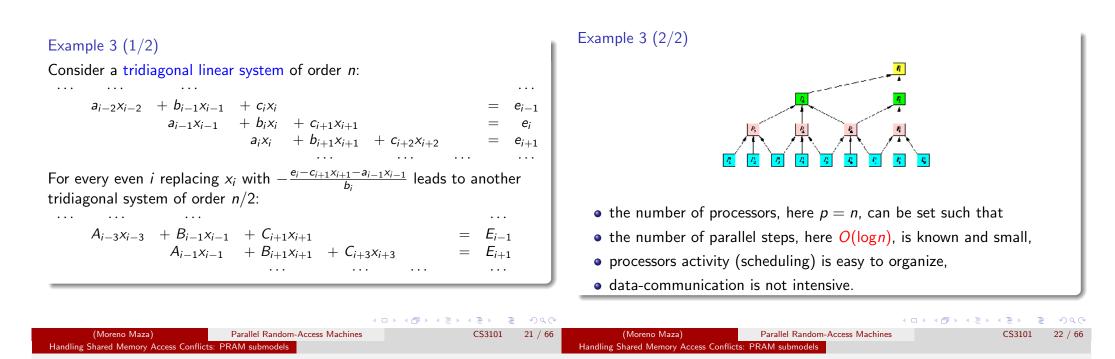

# Handling Shared Memory Access Conflicts (5/18)

### Example 5: statement

On a CREW-PRAM Machine, what does the pseudo-code do?

```

A[1..6] := [0,0,0,0,0,1];

for each 1 <= step <= 5 do</pre>

for each 1 <= i <= 5 do in parallel

A[i] := A[i] + A[i+1]; // done by processor #i

print A;

```

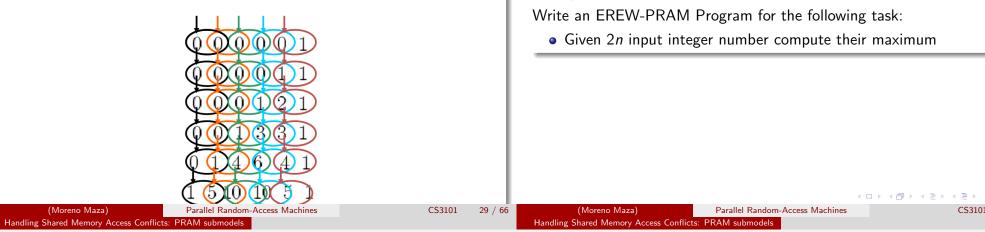

#### Handling Shared Memory Access Conflicts: PRAM submodels

# Handling Shared Memory Access Conflicts (6/18)

### Example 5: solution

(Moreno Maza)

- No data races occur thanks to the execution model (the 3-phasis cycle) and CREW handling.

- On an actual computer, there would be data races and an uncertain result, that is, a non-deterministic answer.

# Handling Shared Memory Access Conflicts (8/18)

Parallel Random-Access Machines

# Handling Shared Memory Access Conflicts (9/18)

# Handling Shared Memory Access Conflicts (7/18)

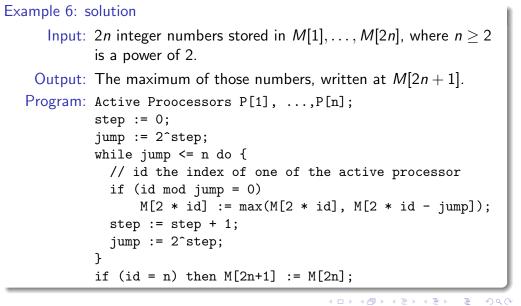

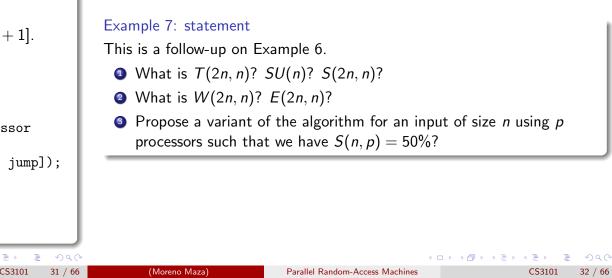

Example 6: statement

# Handling Shared Memory Access Conflicts (10/18)

### Example 7: solution

- 2  $n\log(n)$ ,  $n/(n\log(n))$ .

- Algorithm:

- Use  $p := n/\log(n)$  processors, instead of n.

- Make each of these p processors computes serially the maximum of log(n) numbers. This requires log(n) parallel steps and has total work n.

- Run the previous algorithm on these p "local maxima". This will take log(p) ∈ O(log(n)) steps with a total work of plog(p) ∈ O((n/log(n))log(n)).

- Therefore the algorithm runs in at most  $2\log(n)$  parallel steps and uses  $n/\log(n)$  processors. Thus, we have S(n, p) = 50%.

# Handling Shared Memory Access Conflicts (11/18)

### Example 8: statement

Write a COMMON CRCW-PRAM Program for the following task:

- Given *n* input integer number compute their maximum.

- And such that this program runs essentially in constant time, that is, O(1).

| (Moreno Maza)<br>Handling Shared Memory Access Conflicts | Parallel Random-Access Machines | CS3101 | 33 / 66           | (Moreno Maza)<br>Handling Shared Memory Access Conflic | Parallel Random-Access Machines | CS3101 | 34 / 66 |

|----------------------------------------------------------|---------------------------------|--------|-------------------|--------------------------------------------------------|---------------------------------|--------|---------|

| Handling Shared Memory Access Conflicts (12/18)          |                                 |        | Handling Shared M | lemory Access Conflic                                  | cts (13/18)                     |        |         |

|                                                          |                                 |        |                   |                                                        |                                 |        |         |

### Example 8: solution

# Example 9: statement

This is a follow-up on Example 6.

- What is  $T(n, n^2)$ ? SU(n)?  $S(n, n^2)$ ?

- **2** What is  $W(n, n^2)$ ?  $E(n, n^2)$ ?

CS3101 35 / 6

# Handling Shared Memory Access Conflicts (14/18)

# Handling Shared Memory Access Conflicts (15/18)

# Example 9: solution

- **0** *O*(1), *n*, *n*.

- **2**  $n^2$ , 1/n.

### Example 10: statement

Write an EREW-PRAM Program for the following task:

- Given two polynomials of degree less than n-, say  $a = a_{n-1}x^{n-1} + \cdots + a_1X + a_0$  and  $b = b_{n-1}x^{n-1} + \cdots + b_1X + b_0$ compute their product in parallel time  $o(\log_2(n))$ .

- We may make assumptions of the form "n is a power of 2".

| (Moreno Maza) Parallel Random-Access Machines CS3101 37 / 66<br>Handling Shared Memory Access Conflicts: PRAM submodels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Handling Shared Memory Access Conflicts (16/18)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Handling Shared Memory Access Conflicts $(17/18)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| <pre>Example 10: solution (1/3) Input: Tow polynomials a = a<sub>n-1</sub>x<sup>n-1</sup> + + a<sub>1</sub>X + a<sub>0</sub> and             b = b<sub>n-1</sub>x<sup>n-1</sup> + + b<sub>1</sub>X + b<sub>0</sub> such that M[i] holds a<sub>i-1</sub>             and M[n+i] holds b<sub>i-1</sub> for 1 ≤ i ≤ n and n is a power of 2. Output: Their product. Program: Active Proocessors P[1],,P[n^2];             // id the index of one of the active processor             i := ((id -1) mod n) + 1;             j := ((id -1) quo n) + 1;             M[2n + id] := M[i] * M[n + j];  The problem in the above code is that we have to sum up all M[2n + i] * M[2n + j] contributing to the same coefficient of the product. Indeed, we need to write these products in consecutive memory location to sum them conveniently.</pre> | <ul> <li>Example 10: solution (2/3)</li> <li>Observe that a ⋅ b has 2n - 1 coefficients.</li> <li>The number n<sub>d</sub> of terms contributing to X<sup>d</sup> satisfies <ul> <li>n<sub>d</sub> = </li> <li>d + 1 for 0 ≤ d ≤ n - 1,</li> <li>2n - d for n ≤ d ≤ 2n - 2.</li> </ul> </li> <li>Observe that 1 ≤ n<sub>d</sub> ≤ n for all 0 ≤ d ≤ 2n - 2.</li> <li>For each d ∈ {0,, 2n - 2}, we allocate n slots (we assume that the memory allocator initializes them to zero) to write the n<sub>d</sub> terms contributing to X<sup>d</sup>.</li> <li>More precisely, M[(2 * n) + (d * n) + i + 1] stores the product M[i + 1] * M[n + j + 1] if d = i + j.</li> </ul> |

| (Moreno Maza) Parallel Random-Access Machines CS3101 39 / 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (Moreno Maza) Parallel Random-Access Machines CS3101 40 / 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Handling Shared Memory Access Conflicts (18/18)                                                                                                                                                                                                                                  | Plan                                                                                                                                                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Example 10: solution (3/3)                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                        |

| Active Proocessors P[1],,P[n^2];<br>// id the index of one of the active processor                                                                                                                                                                                               | 1 The PRAM Model                                                                                                                                                                                                                                                                       |

| <pre>i := ((id -1) mod n); j := ((id -1) quo n);<br/>// Observe that i and j are now in 0(n-1)<br/>d := i+j;</pre>                                                                                                                                                               | 2 Performance counters                                                                                                                                                                                                                                                                 |

| M[(2 * n) + (d * n) + i + 1] := M[i+1] * M[n + j + 1];                                                                                                                                                                                                                           | 3 Handling Shared Memory Access Conflicts: PRAM submodels                                                                                                                                                                                                                              |

| • After this point <i>n</i> processors can work together on a parallel reduction for each <i>d</i> .                                                                                                                                                                             | 4 Simulation of large PRAMs on small PRAMs                                                                                                                                                                                                                                             |

| <ul> <li>Since d ∈ {0,, 2n − 2}, each processor will participate to at most 2 parallel reductions.</li> </ul>                                                                                                                                                                    | 5 Comparing the Computational Power of PRAM Submodels                                                                                                                                                                                                                                  |

| • For simplicity, the code should make each processor work on 2 parallel reductions.                                                                                                                                                                                             | 6 More PRAM algorithms and exercies                                                                                                                                                                                                                                                    |

| • Hence additional "zero" slots must be added.                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                        |

| (Moreno Maza) Parallel Random-Access Machines CS3101 41 / 66<br>Simulation of large PRAMs on small PRAMs                                                                                                                                                                         | (Moreno Maza) Parallel Random-Access Machines CS3101 42 / 66<br>Simulation of large PRAMs on small PRAMs                                                                                                                                                                               |

| Simulation of large PRAMs on small PRAMs $(1/3)$                                                                                                                                                                                                                                 | Simulation of large PRAMs on small PRAMs (2/3)                                                                                                                                                                                                                                         |

| Proposition 1                                                                                                                                                                                                                                                                    | Proposition 2                                                                                                                                                                                                                                                                          |

| Let $p' < p$ . Then, any problem that can be solved on a <i>p</i> -processor PRAM in <i>t</i> steps can be solved on a <i>p</i> '-processor PRAM in $t' = O(tp/p')$ steps assuming the same size of shared memory.                                                               | Assume $m' < m$ . Then, any problem that can be solved on a <i>p</i> -processor<br>and <i>m</i> -cell PRAM in <i>t</i> steps can be solved on a max $(p, m')$ -processor and<br>m'-cell PRAM in $t' = O(tm/m')$ steps.                                                                 |

| Proof                                                                                                                                                                                                                                                                            | Proof of Proposition 2 $(1/2)$                                                                                                                                                                                                                                                         |

| In order to reach this result, each of the processors $P'_i$ of the $p'$ -processor PRAM can simulate a group $G_i$ of (at most) $\lceil p/p' \rceil$ processors of the $p$ -processor PRAM as follows. Each simulating processor $P'_i$ simulates one 3-phase cycle of $G_i$ by | • Naturally, the idea is to use the register set of the processors of the <i>m</i> '-cell PRAM in order to compensate the diminution of shared memory.                                                                                                                                 |

| <ul> <li>executing all their READ instructions,</li> </ul>                                                                                                                                                                                                                       | • This is why it is necessary to assume that the <i>m</i> '-cell PRAM has at least <i>m</i> ' processors. (After that, one can use Proposition 1 to save on processors.)                                                                                                               |

| executing all their local COMPUTATIONS,                                                                                                                                                                                                                                          | <ul> <li>Let P<sub>1</sub>,, P<sub>p</sub> be the processors of the <i>m</i>-cell PRAM:</li> </ul>                                                                                                                                                                                     |

| executing all their WRITE instructions.                                                                                                                                                                                                                                          | <ul> <li>We use processors P'<sub>1</sub>,, P'<sub>m''</sub> on the m'-cell PRAM to simulate</li> </ul>                                                                                                                                                                                |

| One can check that, whatever is the model for handling shared memory cell access conflict, the simulating PRAM will produce the same result as the larger PRAM.                                                                                                                  | <ul> <li>We use processors r 1,, r mr on the m cell r with to simulate P<sub>1</sub>,, P<sub>p</sub> where m'' = max(p, m').</li> <li>Moreover, we (mentally) group the m cells of the m-cell PRAM into m' continuous segments S<sub>1</sub>,, S<sub>m'</sub> of size m/m'.</li> </ul> |

| (Moreno Maza) Parallel Random-Access Machines CS3101 43 / 66                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                        |

Simulation of large PRAMs on small PRAMs

Handling Shared Memory Access Conflicts: PRAM submodels

| Simulation of large PRAMs on small PRAMs                                                                                                                                                                                                                                                                           | Comparing the Computational Power of PRAM Submodels                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Simulation of large PRAMs on small PRAMs $(2/3)$                                                                                                                                                                                                                                                                   | Plan                                                                                                                |

| Proof of Proposition 2 $(2/2)$                                                                                                                                                                                                                                                                                     |                                                                                                                     |

| • We use the register set of processor $P'_i$ for simulating the segment $S_i$ , for all $1 \le i \le m'$ .                                                                                                                                                                                                        | 1 The PRAM Model                                                                                                    |

| • We use the shared memory cell $M'[i]$ , for $1 \le i \le m'$ , on the $m'$ -cell PRAM, as an auxiliary memory.                                                                                                                                                                                                   | 2 Performance counters                                                                                              |

| Simulation of one 3-phase cycle of the <i>m</i> -cell PRAM:                                                                                                                                                                                                                                                        | 3 Handling Shared Memory Access Conflicts: PRAM submodels                                                           |

| READ: for all $0 \le k < m/m'$ repeat                                                                                                                                                                                                                                                                              | Simulation of large PRAMs on small PRAMs                                                                            |

| <ol> <li>for all 1 ≤ i ≤ m', the processor P'<sub>i</sub> writes the value of the k-th cell of S<sub>i</sub> into M'[i];</li> <li>for all 1 ≤ i ≤ p, the processor P'<sub>i</sub> reads from the share memory, provided that P<sub>i</sub> would read its value at position congruent to k modulo m/m'.</li> </ol> | <ul> <li>Somparing the Computational Power of PRAM Submodels</li> <li>More PRAM algorithms and exercises</li> </ul> |

| COMPUTE: the local computation of $P_i$ is simulated by $P'_i$ , for all $1 \le i \le p$ .                                                                                                                                                                                                                         |                                                                                                                     |

| WRITE: Analogous to READ.                                                                                                                                                                                                                                                                                          | < ロ > < 団 > < 三 > < 三 > < 三 > < 三 > < 三 > < 三 > < つ < つ < つ < つ < つ < つ < つ < つ < つ <                               |

| (Moreno Maza) Parallel Random-Access Machines CS3101 45 / 66<br>Comparing the Computational Power of PRAM Submodels                                                                                                                                                                                                | (Moreno Maza)Parallel Random-Access MachinesCS310146 / 66Comparing the Computational Power of PRAM Submodels        |

| Comparing the Computational Power of PRAM Submodels                                                                                                                                                                                                                                                                | Comparing the Computational Power of PRAM Submodels                                                                 |

### Remark

By PRAM submodels, we mean either EREW, CREW, COMMON, ARBITRARY or PRIORITY.

### Definition

PRAM submodel A is computationally stronger than PRAM submodel B, written  $A \geq B$ , if any algorithm written for B will run unchanged on A in the same parallel time, assuming the same basic properties.

## Proposition 3

We have:

$\label{eq:prior} \text{PRIORITY} \ \geq \ \text{ARBITRARY} \ \geq \ \text{COMMON} \ \geq \ \text{CREW} \ \geq \ \text{EREW}.$

### Theorem 1

Any polylog time PRAM algorithm is robust with respect to all PRAM submodels.

### Remark

- In other words, any PRAM algorithm which runs in polylog time on one submodel can be simulated on any other PRAM submodel and run within the same complexity class.

- This results from Proposition 3 and Lemma 2.

- Lemma 1 provides a result weaker than Lemma 2 but the proof of the former helps understanding the proof of the latter.

CS3101 47

< 日 > < 同 > < 三 > <

# Lemma 1

Assume PRIORITY CRCW with the priority scheme based trivially on indexing: lower indexed processors have higher priority. Then, one step of *p*-processor *m*-cell PRIORITY CRCW can be simulated by a *p*-processor *mp*-cell EREW PRAM in  $O(\log(p))$  steps.

# Proof of Lemma 1 (1/3)

Naturally, the idea is to

- store all the WRITE (or READ) needs for one cycle in memory

- evaluate their priorities

- execute the instruction of the winner

But there is a trap, we should avoid access conflict also during this simulation algorithm.

| (Moreno Maza) Parallel Random-Access Machine<br>Comparing the Computational Power of PRAM Submodels                                                                                                                                                                                                                                                                                                                                                                                                                      | ←□ → ←□ → ← Ξ → ← Ξ → → へで     CS3101 49 / 66                                                                                                                             | (Moreno Maza) Parallel Random-Access Machines CS3101 50 / 66<br>Comparing the Computational Power of PRAM Submodels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Comparing the Computational Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | of PRAM Submodels                                                                                                                                                         | Comparing the Computational Power of PRAM Submodels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <ul> <li>Proof of Lemma 1 (2/3)</li> <li>(1) Each PRIORITY processor P<sub>k</sub> is simulated for all 1 ≤ k ≤ p.</li> <li>(2) Each shared memory cell M[i], for all i = <ul> <li>is simulated by an array of p shared memor of EREW,</li> <li>M'[i,1] plays the role of M[i],</li> <li>M'[i,2],,M'[i,p] are auxiliary cells us <ul> <li>initially empty,</li> <li>M'[i,1],,M'[i,p] are regarded as the T<sub>i</sub> with p leaves and height [log(p)]; is leaf row of T<sub>i</sub>.</li> </ul> </li> </ul></li></ul> | 1,, <i>m</i> , of PRIORITY<br>hory cells $M'[i, k], k = 1,, p$<br>ed for resolving conflicts,<br>he rows of a complete binary tree<br>initially, they are regarded as the | <ul> <li>Proof of Lemma 1 (3/3)</li> <li>(3) Simulation of a PRIORITY WRITE substep. Each EREW processor <ul> <li>must find out whether it is the processor with lowest index within the group asking to write to the same memory cell, and if so,</li> <li>must become the group winner and perform the WRITE operation; the other processors of its group just fail and do not write.</li> </ul> </li> <li>This is done as follows: <ul> <li>For all 1 ≤ k ≤ p repeat: if P<sub>k</sub> wants to write into M[i], then P'<sub>k</sub> turns active and becomes the k-th leaf of T<sub>i</sub>.</li> <li>Each active left processor stores its ID into the parent cell in its tree, marks it as occupied and remains active.</li> <li>Each active right processor checks its parent cell: if it is empty, then it stores its ID there and remains active, otherwise it becomes inactive.</li> <li>This is repeated one row after another from bottom to top in T<sub>i</sub>, in [log(p)] iterations.</li> </ul> </li> <li>The process who managed to reach the root of T<sub>i</sub>, becomes the winner and can WRITE.</li> </ul> |

| (Moreno Maza) Parallel Random-Access Machine                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | s CS3101 51 / 66                                                                                                                                                          | (Moreno Maza) Parallel Random-Access Machines CS3101 52 / 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

# Lemma 2

One step of PRIORITY CRCW with p processors and m shared memory cells by an EREW PRAM in  $O(\log(p))$  steps with p processors and m + pshared memory cells.

# Proof of Lemma 2 (1/3)

- **(**) Each PRIORITY processor  $P_k$  is simulated by EREW processor  $P'_k$ .

- **2** Each PRIORITY cell M[i] is simulated by EREW cell M'[i].

- $\bigcirc$  EREW uses an auxiliary array A of p cells.

- If  $P_k$  wants to access M[i], then processor  $P'_k$  writes pair (i, k) into A[k].

- **(a)** If  $P_k$  does not want to access any PRIORITY cell, processor  $P'_k$  writes (0, k) into A[k].

- 6 All p processors sort the array A into lexicographic order using (logp)-time parallel sort.

|                                                     | < □ >                           | <ul> <li>&lt; □ &gt; &lt; □ &gt; &lt; □ &gt; &lt; □</li> </ul> | - <b>^</b> ~ ~                                      |                   |                                 | ▲□▶ ▲□▶ ▲□▶ ▲□▶ | ≣ ୬ <b>୯</b> ୯ |

|-----------------------------------------------------|---------------------------------|----------------------------------------------------------------|-----------------------------------------------------|-------------------|---------------------------------|-----------------|----------------|

| (Moreno Maza)                                       | Parallel Random-Access Machines | CS3101                                                         | 53 / 66                                             | (Moreno Maza)     | Parallel Random-Access Machines | CS3101          | 54 / 66        |

| Comparing the Computational Power of PRAM Submodels |                                 |                                                                | Comparing the Computational Power of PRAM Submodels |                   |                                 |                 |                |

| Comparing the Computational Power of PRAM Submodels |                                 |                                                                |                                                     | Comparing the Cor | nputational Power c             | of PRAM Submo   | dels           |

# Proof of Lemma 2 (2/3)

- Each  $P'_k$  appends to cell A[k] a flag f defined as follows

- f = 0 if the first component of A[k] is either 0 or it is the same as the first component of A[k-1].

- f = 1 otherwise.

- **2** Further steps differ for simulation of WRITE or READ.

# **PRIORITY WRITE:**

- Each  $P'_k$  reads the triple (i, j, f) from cell A[k] and writes it into A[i]

- 2 Each  $P'_k$  reads the triple (i, k, f) from cell A[k] and writes into M[i] iff f = 1.

# Comparing the Computational Power of PRAM Submodels

# Proof of Lemma 2 (3/3)**PRIORITY READ:**

- **1** Each  $P'_k$  reads the triple (i, j, f) from cell A[k].

- 2 If f = 1, it reads value  $v_i$  from M[i] and overwrites the third component in A[k] (the flag f) with  $v_i$ .

- In at most log *p* steps, this third component is then distributed in subsequent cells of A until it reaches either the end or an element with a different first component.

- Each  $P'_k$  reads the triple  $(i, j, v_i)$  from cell A[k] and writes it into A[i].

- **5** Each  $P'_k$  who asked for a READ reads the value  $v_i$  from the triple  $(i, k, v_i)$  in cell A[k].

# Parallel scan (1/5)

# 1 The PRAM Model

2 Performance counters

- 3 Handling Shared Memory Access Conflicts: PRAM submodels

- ④ Simulation of large PRAMs on small PRAMs

- 5 Comparing the Computational Power of PRAM Submodels

# 6 More PRAM algorithms and exercies

- Another common and important data parallel primitive.

- This problem seems inherently sequential, but there is an efficient parallel algorithm.

- Applications: sorting, lexical analysis, string comparison, polynomial evaluation, stream compaction, building histograms and data structures (graphs, trees, etc.) in parallel.

|                                   |                                 | ▶ ★ 글 ▶ ★ 글 ▶ 글 | うくで                               |                       | 4                               | (ㅁ`ヾ@`ヾ``、、... | গ প ৫   |

|-----------------------------------|---------------------------------|-----------------|-----------------------------------|-----------------------|---------------------------------|----------------|---------|

| (Moreno Maza)                     | Parallel Random-Access Machines | CS3101          | 57 / 66                           | (Moreno Maza)         | Parallel Random-Access Machines | CS3101         | 58 / 66 |

| More PRAM algorithms and exercise |                                 |                 | More PRAM algorithms and exercise |                       |                                 |                |         |

|                                   | 、<br>、                          |                 |                                   |                       |                                 |                |         |

| Parallel scan (2/5                |                                 |                 |                                   | Parallel scan $(3/5)$ |                                 |                |         |

{

}

}

- Let S be a set, let  $+: S \times S \to S$  be an associative operation on S with 0 as identity. Let  $A[0 \cdots n-1]$  be an array of n elements of S.

- Tthe *all-prefixes-sum* or *inclusive scan* of A computes the array B of n elements of S defined by

$$B[i] = \begin{cases} A[0] & \text{if } i = 0\\ B[i-1] + A[i] & \text{if } 0 < i < n \end{cases}$$

• The exclusive scan of A computes the array B of n elements of S:

$$C[i] = \begin{cases} 0 & \text{if } i = 0 \\ C[i-1] + A[i-1] & \text{if } 0 < i < n \end{cases}$$

- An exclusive scan can be generated from an inclusive scan by shifting the resulting array right by one element and inserting the identity.

- Similarly, an inclusive scan can be generated from an exclusive scan.

- We shall focus on exclusive scan.

・ロット (雪) (日) (日)

3

Parallel Random-Access Machines

Here's a sequential algorithm for the exclusive scan.

for(int j = 1; j < length; ++j)</pre>

void scan( float\* output, float\* input, int length)

output[j] = input[j-1] + output[j-1];

output[0] = 0; // since this is a prescan, not a scan

э.

| More PRAM algorithms and exercies                                                                 | More PRAM algorithms and exercies                                                                                                                                                                                                                           |

|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parallel scan (4/5)                                                                               | Parallel scan (5/5)                                                                                                                                                                                                                                         |

| <text><equation-block><text></text></equation-block></text>                                       | <pre>Input: Elements located in M[1],, M[n], where n is a power of 2.<br/>Output: The n prefix sums located in M[n + 1],, M[2n].<br/>Program: Active Proocessors P[1],, P[n]; // id the active proof<br/>for d := 1 to log(n) do<br/>if d is odd then</pre> |

| (Moreno Maza) Parallel Random-Access Machines CS3101 61 / 66<br>More PRAM algorithms and exercies | (Moreno Maza) Parallel Random-Access Machines CS3101 62 / 66<br>More PRAM algorithms and exercies                                                                                                                                                           |

| Mysterious algorithm $(1/5)$                                                                      | Mysterious algorithm $(2/4)$                                                                                                                                                                                                                                |

• What does the following CREW-PRAM algorithm compute?

```

Input: n elements located in M[1], \ldots, M[n], where n \ge 2 is a

power of 2.

Output: Some values in located in M[n + 1], \ldots, M[2n].

Program: Active Proocessors P[1], ...,P[n];

// id the index of one of the active processor

M[n + id] := M[id];

M[2 n + id] := id + 1;

for d := 1 to log(n) do

if M[2 n + id] < n then {

j := M[2 n + id];

M[n + j] := M[n + id] + M[n + j];

M[2 n + id] := M[2 n + j];

}

}

```

• Analyze its efficiency.

| (Moreno | Maza' | ) |

|---------|-------|---|

-

<ロト < 同ト < ヨト < ヨト

| More PRAM algorithms and exe | ercies                |                | More PRAM alg       | orithms and exercies            |    |              |

|------------------------------|-----------------------|----------------|---------------------|---------------------------------|----|--------------|

| Mysterious algorithm $(3/4)$ | )                     |                | Mysterious algorith | m (4/4)                         |    |              |

|                              |                       |                |                     |                                 |    |              |

|                              |                       |                |                     |                                 |    |              |

|                              |                       |                |                     |                                 |    |              |

|                              |                       | 7              |                     |                                 |    | ,            |

|                              |                       | ,              |                     |                                 |    | ,            |

|                              |                       |                |                     |                                 |    |              |

|                              |                       |                |                     |                                 |    |              |

|                              |                       |                |                     |                                 |    |              |

|                              |                       |                |                     |                                 |    |              |

|                              |                       | ・ 目 うへで        |                     |                                 |    |              |

| (Moreno Maza) Parallel R     | andom-Access Machines | CS3101 65 / 66 | (Moreno Maza)       | Parallel Random-Access Machines | CS | 3101 66 / 66 |