#### CS3350B Computer Architecture Winter 2015

#### **Lecture 5.4: Combinational Logic Blocks**

Marc Moreno Maza

www.csd.uwo.ca/Courses/CS3350b

[Adapted from lectures on *Computer Organization and Design*, Patterson & Hennessy, 5<sup>th</sup> edition, 2013]

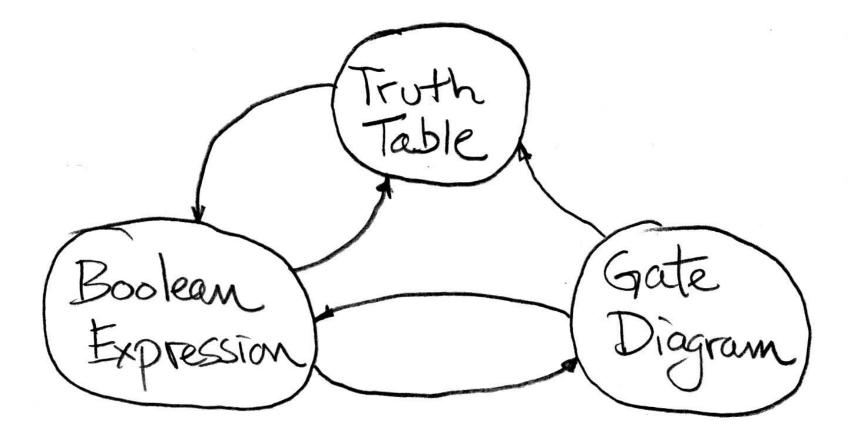

#### Review

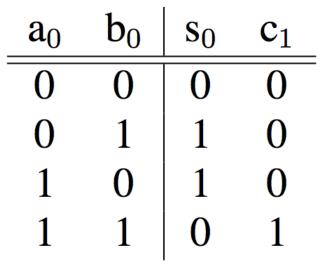

Use this table and techniques we learned to transform from 1 to another

## Plan

- Data Multiplexors

- Arithmetic and Logic Unit

- Adder/Subtractor

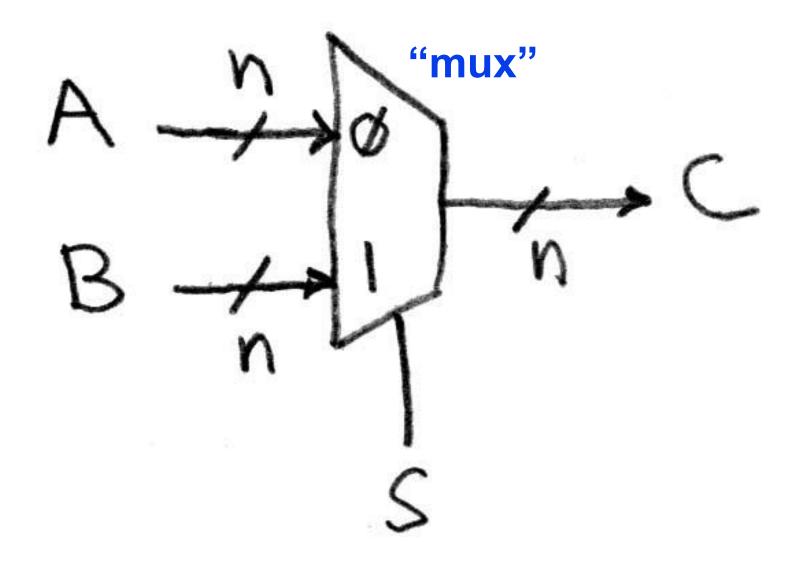

## Data Multiplexor (here 2-to-1, n-bit-wide)

#### N instances of 1-bit-wide mux

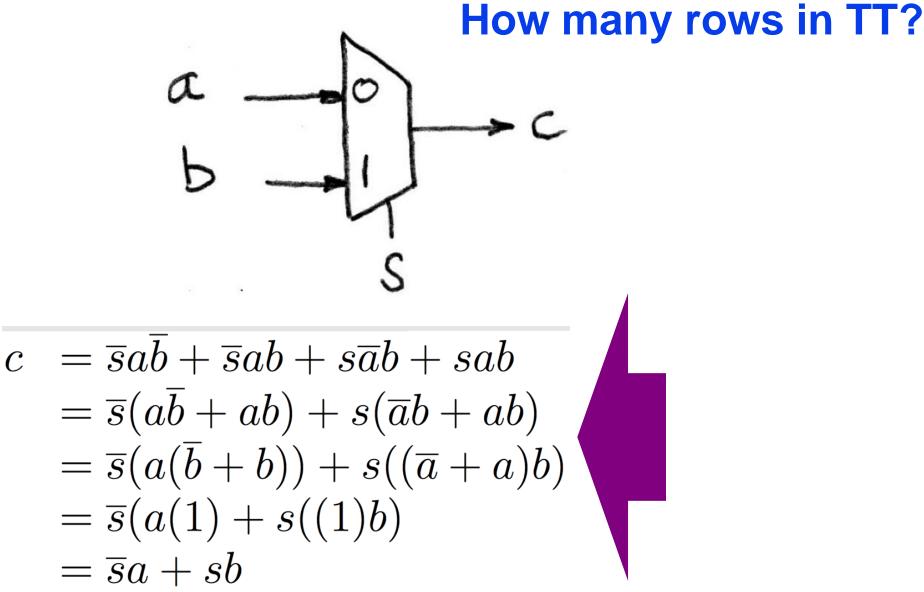

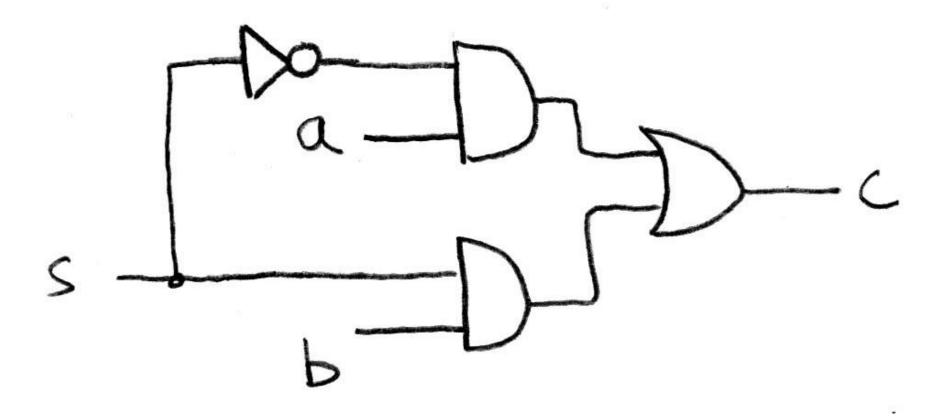

#### How do we build a 1-bit-wide mux?

$\overline{s}a + sb$

6

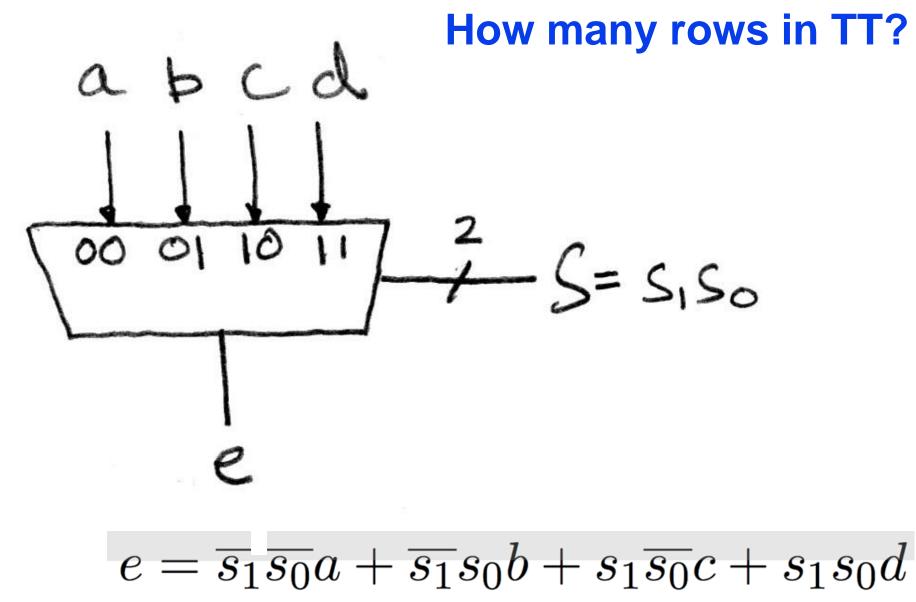

#### **4-to-1 Multiplexor?**

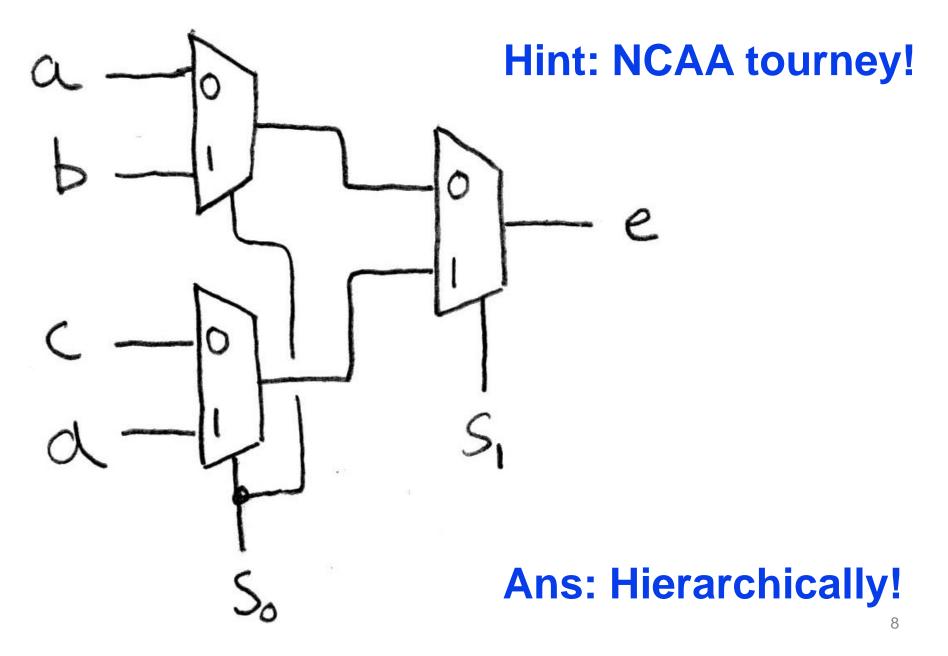

#### Is there any other way to do it?

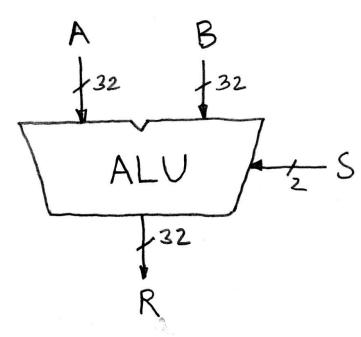

### **Arithmetic and Logic Unit**

- Most processors contain a special logic block called "Arithmetic and Logic Unit" (ALU)

- We'll show you an easy one that does ADD, SUB, bitwise AND, bitwise OR

when S=00, R=A+B when S=01, R=A-B when S=10, R=A AND B when S=11, R=A OR B

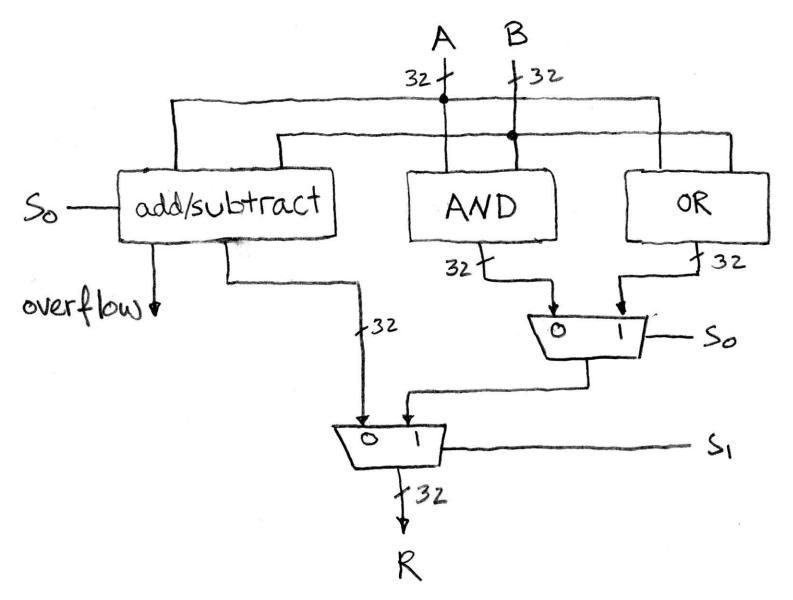

#### **Our simple ALU**

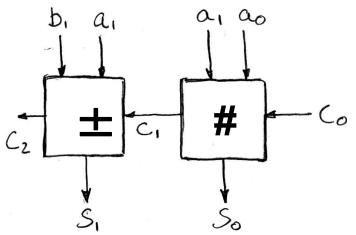

#### **Adder/Subtracter Design -- how?**

- Truth-table, then determine canonical form, then minimize and implement as we've seen before

- Look at breaking the problem down into smaller pieces that we can cascade or hierarchically layer

#### Adder/Subtracter – One-bit adder LSB...

|   | $a_3$ | $a_2$ | $a_1$ | $a_0$                 |

|---|-------|-------|-------|-----------------------|

| + | $b_3$ | $b_2$ | $b_1$ | $b_0$                 |

| · | $s_3$ | $s_2$ | $s_1$ | <b>s</b> <sub>0</sub> |

$$s_0 = c_1 = c_1$$

#### Adder/Subtracter – One-bit adder (1/2)...

|   |                       |                |                       |                |   | $\mathbf{a}_i$ | $\mathbf{b}_i$ | $\mathbf{c}_i$ | $\mathbf{s}_i$ | $\mathbf{c}_{i+1}$ |

|---|-----------------------|----------------|-----------------------|----------------|---|----------------|----------------|----------------|----------------|--------------------|

|   |                       |                |                       |                |   | 0              | 0              | 0              | 0              | 0                  |

|   | 0                     | 0              |                       |                |   | 0              | 0              | 1              | 1              | 0                  |

|   | $a_3$                 |                | 1                     | $a_0$          |   | 0              | 1              |                | 1              | 0                  |

| + | $b_3$                 | $b_2$          | $ b_1 $               | $b_0$          |   | 0              | 1              | 1              | 0              | 1                  |

|   | <b>S</b> <sub>3</sub> | $\mathbf{s}_2$ | <b>S</b> <sub>1</sub> | S <sub>0</sub> | - | 1              | 0              | 0              | 1              | 0                  |

|   | 0                     | 2              |                       | j              |   | 1              | 0              | 1              | 0              | 1                  |

|   |                       |                |                       |                |   | 1              | 1              | 0              | 0              | 1                  |

|   |                       |                |                       |                |   | 1              | 1              | 1              | 1              | 1                  |

|   |                       |                |                       |                |   |                |                |                | I              |                    |

|   |                       |                |                       |                |   |                |                |                |                |                    |

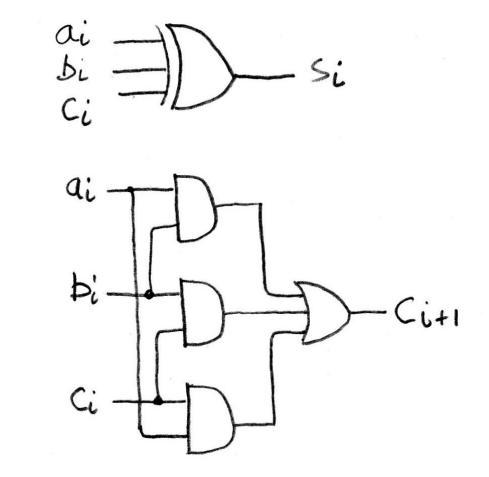

#### Adder/Subtracter – One-bit adder (2/2)...

$$s_i = \operatorname{XOR}(a_i, b_i, c_i)$$

$$c_{i+1} = \operatorname{MAJ}(a_i, b_i, c_i) = a_i b_i + a_i c_i + b_i c_i$$

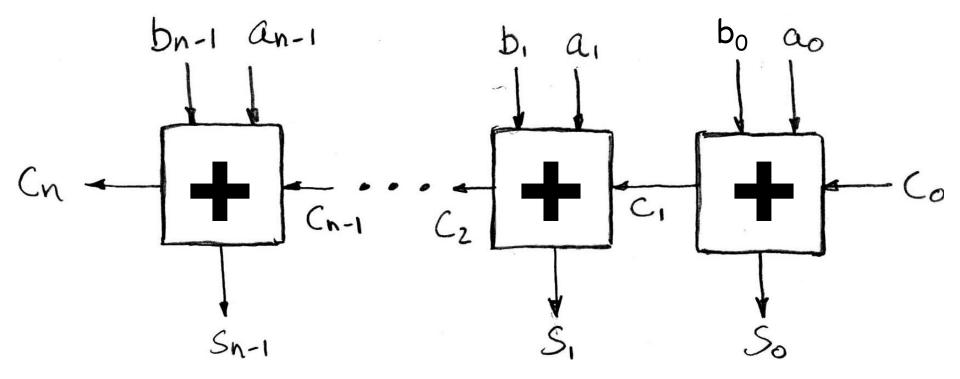

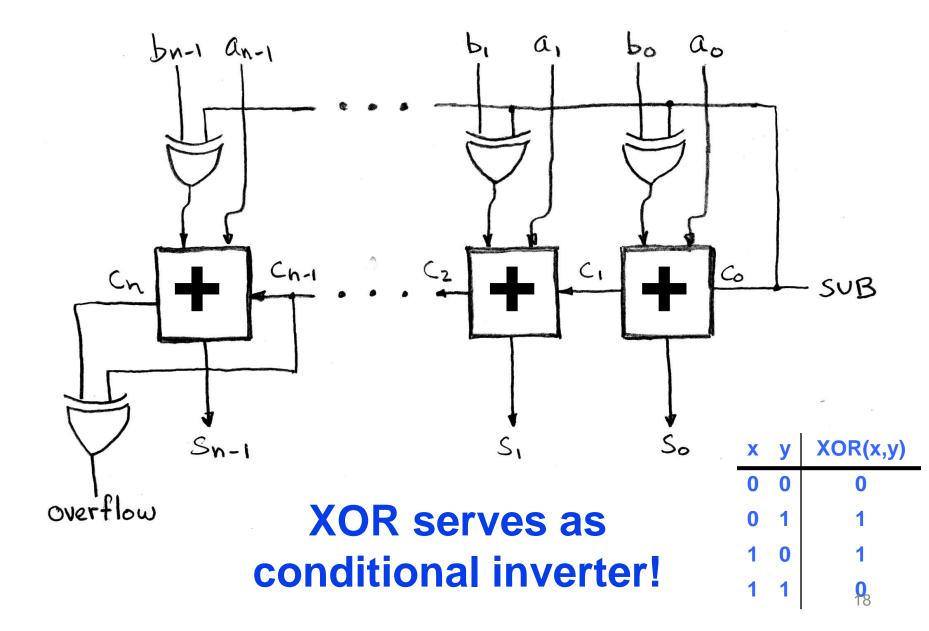

#### **N 1-bit adders** $\Rightarrow$ **1 N-bit adder**

## What about overflow? Overflow = $c_n$ ?

# What about overflow?

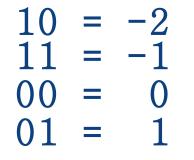

- Consider a 2-bit signed # & overflow:

- $\cdot 10 = -2 + -2$  or -1 $\cdot 11 = -1 + -2$  only

- $\bullet 00 = 0$  NOTHING!

- $\bullet 01 = 1 + 1$  only

- Highest adder

- $C_1 = Carry-in = C_{in}, C_2 = Carry-out = C_{out}$

- No  $C_{out}$  or  $C_{in} \Rightarrow$  NO overflow!

- What  $\cdot C_{in}$ , and  $C_{out} \Rightarrow NO$  overflow!

- $C_{in}$ , but no  $C_{out} \Rightarrow A,B$  both > 0, overflow!  $C_{out}$ , but no  $C_{in} \Rightarrow A,B$  both < 0, overflow! op?

What about overflow?

Consider a 2-bit signed # & overflow:

Overflows when...

•  $C_{in}$ , but no  $C_{out} \Rightarrow A,B$  both > 0, overflow! •  $C_{out}$ , but no  $C_{in} \Rightarrow A,B$  both < 0, overflow!

# overflow = $c_n \operatorname{XOR} c_{n-1}$

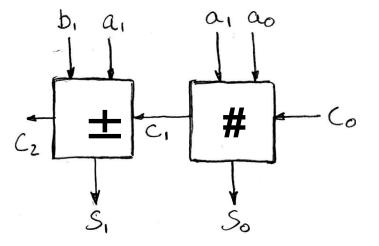

#### **Extremely Clever Subtractor**

#### "And In conclusion..."

- Use muxes to select among input

- S input bits selects 2<sup>S</sup> inputs

- Each input can be n-bits wide, indep of S

- Can implement muxes hierarchically

- ALU can be implemented using a mux

- Coupled with basic block elements

- N-bit adder-subtractor done using N 1bit adders with XOR gates on input

- XOR serves as conditional inverter